# Performance Evaluation for Parallel Systems: A Survey

Lei Hu and Ian Gorton

Department of Computer Systems

School of Computer Science and Engineering

University of NSW, Sydney 2052, Australia

E-mail: {lei, iango}@cse.unsw.edu.au

UNSW-CSE-TR-9707 — October 1997

#### **Abstract**

Performance is often a key factor in determining the success of a parallel software system. Performance evaluation techniques can be classified into three categories: measurement, analytical modeling, and simulation. Each of them has several types. For example, measurement has software, hardware, and hybrid; simulation has discrete event, trace/execution driven, Monte Carlo; and analytical modeling has queueing network, Petri net, etc.. This paper systematically reviews various techniques, and surveys work done in each category. Also addressed and discussed are other issues related to performance evaluation. These issues include how to select metrics and proper techniques that are well suited for the particular development stage, how to construct a good model, and how to perform workload characterization. We also present fundamental laws and scalability analysis techniques. While many techniques discussed are common in both sequential and parallel system performance evaluation, our focus is on the parallel systems.

#### 1 Introduction

Computer systems become more and more powerful. Many manufacturers design and implement various architectures ranging from microcomputers to supercomputers according to different application demands. Parallel computer architectures arise for many reasons. One of them is probably the limits imposed by the laws of physics on the development of semiconductor technology (see for example [Liu82]). Applications are getting more and more sophisticated: some problems must be solved within a limited amount of time. Weather forecasting is such a time-critical example. This forces computer scientists to seek innovative architectures and exploit parallelism in order to meet the demands of high speed computing.

Different systems have different architectures. Based on notions of instruction stream and data stream, Flynn [Flynn72] classified various computer architectures into four categories: SISD, SIMD, MIMD, and MISD. Of the four machine models, MIMD is most widely used for constructing machines for general-purpose computations. MIMD parallel computers can further be classified into share-memory multiprocessors and message-passing multicomputers.

With these different architectures, a problem that arises immediately is how to choose a system for a particular problem. Selecting a proper architecture for an application is problem oriented. One architecture that suits one kind of problems may not at all suit another. After a particular architecture is chosen, the following questions may be asked. How will the system perform? What criteria should be used to evaluate the performance? What techniques can/should we use to get the performance values? To answer these questions is the objective of performance evaluation.

According to [Ferrari86], performance evaluation dates back to 1965, when Alan Scherr submitted his Ph.D. thesis. Since then, great progress has been made in this area. It has become a distinct discipline independent of others, such as computer architecture, system organization, operating system, and so forth. Many textbooks are devoted to this subject (see for example [Drummond73; Sauer81; Jain91]).

Performance evaluation can be defined as assigning quantitative values to the indices of the performance of the system under study. So, what is performance?

To answer this question is not easy, for performance involves many aspects. Here, we do not mean to give our definition, for many authors have given different definitions from different perspectives (e.g., [Doherty70; Graham73]. In what follows, we try to list some factors that must be considered: *functionality*, reliability, speed, and economicity. First, functionality is the most important. Any successful system must do what its designer wants it to do. If the system cannot meet this basic demand, it is meaningless to talk about any other things. Second, a system must be as reliable as possible. Given a service request to a system, there exist two possible outcomes: the system services the request correctly or incorrectly. If it fails to service correctly, the probability that error occurs should be studied. If the probability is too high and cannot meet the design specification, the system should be redesigned or improved until the error probability limits to a reasonable level. Third, if a system can service the requests made to it correctly, how fast and efficient it completes the work becomes important (the speed factor). Because functionality and reliability are two basic issues that are often considered and solved by any system designer at a very early stage of the design life-cycle, speed becomes the most frequent research topic in the performance evaluation community. Speed is often reflected by response time and throughput rate; and efficiency is often reflected by utilization. Finally, a system is always designed and implemented to give its services at a given cost. Given a specification, how to design and implement the system at the lowest cost is what economicity should consider.

To evaluate the performance of a system or to compare two or more systems, one must first choose some criteria. These criteria are called *metrics*. Different metrics may result in totally different performance values. Hence, selecting proper metrics to fairly evaluate the performance of a system is difficult [Jain91]. To know metrics, their relationships and their effects on performance parameters is the first step in performance studies. Next, selecting proper *workload* is almost equally important. A system is

often designed to work in a particular environment with some workload. It is not proper to study the performance without considering the workload.

After choosing proper metrics and workload, one must consider what technique or techniques should be used. Generally, there are three techniques commonly used in performance evaluation. They are *measurement, simulation* and *analytical modeling*. All these techniques play equally important roles in performance studies. Each technique has its own advantages and disadvantages. The precision of the results obtained by each technique often varies from one technique to another. It is not fair to say that one is better than another. To select a technique or techniques to evaluate a system, many factors must be taken into consideration. One must have a clear idea that what goal he/she wants to achieve and at what stage the technique would be used. For example, at the early design stage when the system has not yet been constructed, measurement is obviously impossible, instead, a simple analytical model is practical. As the design process goes on, more and more details about the system are obtained. At this stage, simulation or more sophisticated analytical modeling techniques could be used. Finally, when the system design has been completed and a real system constructed, measuring becomes possible. Quite often, to make the evaluation results more convincing to the system's user, these techniques can be used together.

In the literature, there have appeared a number of excellent survey papers which review the work in a particular aspect discussed above. For example, [Plattner81] and [Power83] are program execution monitor survey papers. Plattner and Nievergelt survey the development of program execution monitors, and discuss basic concepts and requirements, design considerations for monitoring languages, and implementation and timing aspects. Power focuses on program execution monitoring tools. He discusses the design issues and a wide variety of techniques used by existing monitors. In addition, a new program execution monitor is presented, and the design and use of this new monitor are discussed. [Calzarossa93] discusses several methodologies and techniques for constructing workload models in terms of different system architectures, such as centralized systems, network-based systems and multiprocessor systems. [Trivedi94] addresses the analytical modeling techniques including Markov reward models, stochastic Petri net models, and hierarchical and approximate models. Various tools designed to solve these models for performance evaluation studies are also presented and described.

In this paper, we intend to address all the issues that a performance analyst must consider, review and compare in some detail typical techniques applied to performance evaluation, and survey some recent work done in this area. Although many techniques are common in both sequential and parallel system performance evaluation, our focus is on the parallel systems.

The paper is organized as follows. In section 2, we discuss some general issues that must be considered first in performance studies. These issues include what should be considered in modeling, and how to choose proper metrics and appropriate techniques. We also describe advantages and disadvantages of each technique in terms of different conditions the techniques are used. In section 3, we describe several well-known laws such as speedup, isoefficiency, scalability, and so on. These laws are often used in direct analysis of performance. Some commonly used metrics are also introduced. Section 4 describes workload characterization. Mainly, several statistical analysis techniques are introduced; their use in recent workload characterization research is also reviewed. Subsequent sections, sections 5, 6, 7, are dedicated to three different techniques in performance evaluation studies. They are *measurement*, *analytical modeling*, and *simulation*. Each of these sections are further divided into several subsections according to different types of each technique. Finally, section 8 concludes the paper by summarizing the main points addressed through this paper.

#### 2 General Issues

#### 2.1 Modeling

To study a system, as the first step, we must construct a model representing the system under study. We

then research the system's behavior and get knowledge about the system by solving the model using either simulation or theoretical analysis. This method is applicable to any branch of natural science and social science. Performance evaluation is no exception.

A model for a system can informally be defined as "a collection of attributes and a set of rules that govern how these attributes interact" [Mullender93].

Constructing a good model that is really useful to the problem requires many careful considerations and much hard work. A good model has at least two features. First, it must well describe the behavior of a system, and should be as accurate as possible. Second, it must be as simple as possible to solve. The first feature requests that the model include all the necessary details that define the behavior; and the second requests that the model exclude as many parameters as possible. These two features contradict each other. It is the dilemma faced by any practitioner. Including too many parameters may lead to an accurate but too complicated or even unsolvable model. An overly complicated model costs too much to be solved, and an unsolvable model is completely useless to the problem, however accurate it is. Hence, great care should be taken in selecting parameters and a reasonable trade-off should be made.

Before working on it, one must have a clear idea about what the performance study is for, what results are of interest, and what attributes of the system are to be studied. Simply put, what goal is to be achieved? Different situations may have different goals; and different goals may produce different models. Thus, careful examination and full understanding of the problem is necessary.

A model is to a system what a map is to a road system. A model is only representing the system, not the system itself, and it is obtained from various assumptions and different levels of abstraction. Assumptions and abstraction must correspond to the attributes to be studied, emphasize some useful features and ignore some others. The behavior of a system is described by parameters. However, not all the parameters have the same effect on the behavior. It is therefore necessary to list all the parameters first, then carefully examine and compare them, introducing those that most affect the behavior to be studied. That is what we mean by abstraction. This process can lead to a model that just includes the necessary parameters that exactly describe the behavior of interest, and excludes all those that have no or little effect on it.

Once a model has been completed, it can be solved. Quite often the model needs to be validated and modified if the result is too far away from the real world.

Collier [Collier92] summarized the following four steps the modeling process must follow.

- (1) Decide what answers are sought.

- (2) Reduce the complexity of the real world to its essence, eliminating the irrelevant and approximating the unmanageable.

- (3) Translate the essence into a formally defined system within which one can make deductions.

- (4) Test the deductions in the real world, to see if what the model teaches either illuminates or can be applied.

# 2.2 Selecting Metrics

To study the performance of systems or to compare different systems for a given purpose, we must first select some criteria. These criteria are often called metrics in performance evaluation. Different situations need different sets of metrics. Thus, selecting metrics are highly problem oriented. What is more, the same metric may have different weights in different situations. For example, response time is a commonly used metric, which reflects how fast a system completes given services. However, it may receive more attention in a real-time control system than in a network system. The latter may be more interested in such metrics as throughput.

Unfortunately, there is little work which discusses metrics selecting issues in the performance evaluation community [Jain91]. This is not to say that authors ignore the importance of selecting metrics. The probable reason for this phenomenon is that there are countless metrics people may use in various situations: no standard set of metrics has been defined, and no standard technique has been applied. They

greatly vary from problem to problem.

In what follows we discuss some principles and a general process of selecting appropriate metrics. The materials presented in this subsection are mainly from [Jain91]. We hope to see more efforts made and papers published on this subject.

Any system is designed to offer services. Often different services should be examined one by one. For a given service requested to the system, there will be three possible outcomes.

- (1) The system completes the service correctly;

- (2) The system completes the service with error;

- (3) The system fails to perform the service.

After classifying the possible outcomes, the remaining work becomes easier. Each situation need an individual set of metrics. They may be considered separately.

For the first case, the system completes the service correctly, the performance can usually be measured by time-rate-resource metrics, which represent the time used by the system to complete the service, the rate at which the system performs the service, and the resource needed for the system to complete the service. In real examples, they may be response time, throughput, and utilization. These metrics are widely used in performance studies. A great deal of examples can be found in the literature, e.g., [Takahashi87] and [Mailles87].

For the second case, the system completes the service with error, the probability that error occurs should be measured. In many cases, different types of errors need to be classified, and each type studied separately.

For the last case, the system fails to perform the service, again, the probability of failure is of interest. A system often consists of several components. It is sometimes helpful to identify the source of failure. If further examination is necessary, the down component (software or hardware) can be modeled and studied. For example, if the failure comes from the CPU, a simple CPU model can be constructed using two states, an "UP" state and a "DOWN" state. If we assume that the time to failure and the repair time both obey the exponential distribution with parameters  $\lambda$  and  $\mu$  respectively, then this stochastic process is a Markov chain. Some well developed techniques can now be used [Chimento87].

Given a number of metrics candidates, the following three features should further be considered: *low variability*, *nonredundancy*, and *completeness*. High variability may need more efforts to obtain a given degree of statistical confidence. Examining redundancy may reduce the number of metrics; select only one representative of those that have the same effects. For example, in a network router system, which receives packets from the sources and sends them to the destinations, the mean number of packets in the system can be given by the famous Little's Law:

$$\overline{n} = \lambda \overline{\tau}$$

where  $\lambda$  is the mean arrival rate, and  $\bar{\tau}$  is the mean waiting time [Robertazzi94]. Thus, of the two metrics,  $\bar{n}$  and  $\bar{\tau}$ , selecting one is enough. Finally, completeness is obvious. Any selected set of metrics should be able to describe all the possible outcomes related to the performance of interest. Jain's book [Jain91] also presents an example showing the use of the three feathers.

#### 2.3 Performance Evaluation Techniques

There are many techniques that can be used in evaluating performance. Usually these techniques are classified into three categories: measurement, simulation, and analytical modeling [Brewer91; Jain91]. Some authors (e.g., [Ferrari83]) classifies simulation and analytical modeling into one, called modeling technique. This is because whether we use simulation or analytical modeling, we must first construct a model for the system under study. simulation is considered to be one powerful method to solve complex models [Lavenberg83]. This classification is based on the fact that measurement must be done on a real system, i.e., the system to be evaluated must exist and be available, while modeling does not require that. For the convenience of discussion, we use the former classification.

Each of the three techniques has several types. For example, measurement has software, hardware, and hybrid; simulation has discrete event, trace/execution driven, Monte Carlo; and analytical modeling has queueing network, Petri net, etc.. With so many alternatives, selecting one that is suitable for the problem is really difficult, and needs many serious considerations. Below, we discuss the issues that must be taken into account in selecting techniques to solve a problem. These discussions are actually summaries of some representative papers and books (e.g., [Lavenberg83; Jain91; Crovella94; Trivedi94]).

Before doing performance evaluation, considering the following factors is helpful in selecting a proper technique: *stage*, *accuracy*, and *cost*. Perhaps the most important factor one should consider over the others is stage. That is, at what design stage would the performance evaluation be studied, because different stages may need different techniques and accuracy.

Measurement techniques, as the name implies, are based on direct measurements of the system under study using a software monitor or/and hardware monitor. Therefore, the real system must be available. This technique is totally impossible when the system is only at design stage and has not yet been built. Thus measurement is oriented towards *performance tuning*. Simulation and analytical modeling are both based on abstract models instead of real systems. A model can be constructed by abstracting essential features of the design based on appropriate assumptions, before the system is built. Thus both techniques are oriented towards *performance prediction* (although they are sometimes used for tuning). It should be noted that performance prediction at very early stage during the design life-cycle is not only helpful but necessary as well, for this will lead to discovery of potential design flaws which could then be fixed as early as possible, thus avoiding costly improvement or even redesign once the system has been implemented.

It should be pointed out that simulation and analytical modeling can be used throughout the design life-cycle, not only at earlier stages. Often as the design matures and more and more details of the system are obtained, more accurate models can be constructed. In spite of this, analytical modeling techniques are sometimes improper at later stages. This is because at that time the model often involves so many details that it costs too much to solve, or in some cases it is mathematically unsolvable.

Since both simulation and analytical modeling use models, which require simplifications and assumptions and are only approximate representations of reality, approximation errors might be introduced. This is especially true with analytical modeling techniques. To make the model be mathematically solvable, higher level of abstraction and more assumptions must be made. For example, in many analytical models only exponential distributions are allowed for time-distributions (e.g., [Heidelberger83; Mak90]). When simulation is used, this restriction has gone. Many complex non-exponential distributions can easily be used. Briefly, simulation allows more complex and detailed models, thus resulting in more accurate solutions.

Because measurement is directly carried out on a real system, it appears to offer the most accurate results among the three techniques. As a matter of fact, this is not always true. The basic technique of measuring is using instrumentation, which will introduce performance overheads and may also affect the system's dynamic behavior [Jelly94]. This is called instrumentation perturbation. Different kinds of perturbations, direct or indirect, are described by Malony [Malony92]. Besides, the accuracy of measurement also depends on several other things, such as time of the measurement and the workload used. Thus, measurement techniques may offer very accurate data or very inaccurate data, all depending on how well the above factors are treated.

As for the cost, because measurement needs instruments it is the most costly method. Analytical modeling needs nothing, so it is the cheapest one. Simulation goes just in between these two.

To summarize, analytical modeling, with the lowest cost and accuracy, can best be used at earlier stages; simulation, with higher cost and accuracy, can be used at any stage; and measurement, with the highest cost and varying accuracy can only be used after the system has been built.

It is worth mentioning that these techniques should be used together, simultaneously or sequentially, to evaluate a system whenever possible. The results of simulation and analytical modeling would be more convincing if the inputs and parameters are determined based on previous measurement [Jain91]; and

analytical models could be validated by simulations (e.g., [Agarwal92; Menasce92].

# 3 Fundamental Laws and Scalability Analysis

One key problem faced by parallel programmers is how to effectively utilize the processing power provided by the underlying architecture in order to gain performance. Obviously, good performance can easily be achieved when multiple independent sequential job streams are run. It is, however, quite difficult to get good performance from parallel applications [Anderson89]. In the discussions that follow, we assume that the entire computer is devoted to a single parallel application.

In general, as more processors are added to a parallel processing system or used by a parallel algorithm, the proportion of processor time taken to perform useful work diminishes. For example, in the discrete Fourier transform problem, Rayfield and Silverman [Rayfield88] reported that the improvement in speedup keeps diminishing as more processors are used. This phenomenon, or performance loss, is caused by so-called parallel overhead. Rayfield and Silverman attributed this to interprocessor communication and the sequential part of computation. Agarwal [Agarwal92] gave two reasons for the decreasing processor utilization. First, the cost of each memory access increases because network delays increase with system size. Second, as we strive for greater speedups through fine-grain parallelism, the number of network transactions and synchronization delays also increases. A paper by Burkhart and Millen [Burkhart89] discusses and analyzes various sources of performance loss.

This section presents some fundamental laws which research the gain of performance. This gain involves several aspects, not only in time (as with Amdahl's Law), but also in problem size (as with Gustafson's Law) and in the use of resources (as with memory-bounded speedup). These fundamental laws include speedup, scalability, isoefficiency, and so on. These are useful metrics for measuring performance and widely used in the literature. The definitions of these performance measures given by authors from different perspectives are greatly different. Different definitions may lead to different performance results. As we will see later, speedup is such an example. Several formal definitions, such as speedup, efficiency, utilization, etc., can be found in [Lee80]. These are fundamental concepts in parallel processing.

For the convenience of our later discussions, we first give definitions for speedup and efficiency. *Speedup* is defined as the ratio of the execution time of the best possible serial algorithm (on a single processor) to the parallel execution time of the chosen algorithm on a *n*-processor parallel system. Thus, we can write

$$S(n) = \frac{T(1)}{T(n)}$$

Efficiency is defined as the ratio of speedup to the number of processors, or

$$E(n) = \frac{S(n)}{n} = \frac{T(1)}{nT(n)}$$

# 3.1 Parallelism Profile and Asymptotic Speedup

This subsection describes some concepts useful in later discussions on speedup models.

**Parallelism Profile** We define *degree of parallelism* (DOP) as the maximum number of processors used to execute a program at a particular instant in time, given an unbounded number of available processors and other necessary resources. In real systems, the DOP may not always be achievable because of many limitations.

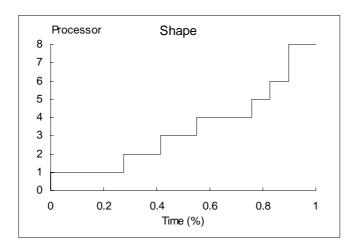

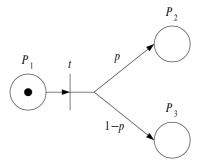

The DOP often changes at different periods of time during the execution cycle. The plot of the DOP over the execution time may be quite helpful in studies. This plot is called *parallelism profile*. Figure 1 shows the parallelism profile of a divide-and-conquer algorithm.

Figure 1. Parallelism profile of a divide-and-conquer algorithm

When *i* processors are busy during a period, we have DOP = i. The maximum DOP in a profile is denoted as *m*. We assume that a parallel processing system consists of *n* homogeneous processor, and n >> m in the ideal case.

The average parallelism is a useful metric in studying speedup and efficiency. It is defined as the average number of processors that are busy during the execution time of the software system in question, given an unbounded number of available processors [Eager89].

According to this definition, the average parallelism can be written as

$$A = \left(\sum_{i=1}^{m} i \cdot t_i\right) / \left(\sum_{i=1}^{m} t_i\right)$$

Eager et al. [Eager89] carefully examine the average parallelism and investigate the tradeoff between speedup and efficiency. They show that

$$S(n) \ge \frac{nA}{n+A-1}$$

and

$$E(n) \ge \frac{A}{n+A-1}$$

S(n) is lower bounded by nA/(n+A-1) and E(n) by A/(n+A-1). We see that if n << A,  $S(n) \to n$ , and if n >> A,  $S(n) \to A$ . It should be noted that the average parallelism measure can only be used in a system without communication overhead.

**Asymptotic Speedup** Let W be the total amount of work of an application,  $W_i$  be the amount of work executed with DOP = i, and  $\Delta$  be the *computing capacity* of each processor, which can be approximated by execution rate, such as MIPS or Mflops [Hwang93]. Thus, we have

$$W_i = i\Delta t_i$$

and

$$W = \sum_{i=1}^{m} W_i = \Delta \sum_{i=1}^{m} i \cdot t_i$$

By denoting the execution time of  $W_i$  on k processors as  $t_i(k)$ , we can write

$$t_{i}(1) = W_{i}/\Delta$$

$$t_{i}(k) = W_{i}/k\Delta$$

$$t_i(\infty) = W_i/i\Delta$$

, for  $1 \le i \le m$

Although an infinite number of processors can be used, the maximum number of processors that can be

used to execute  $W_i$  is still i.

If communication latency and other system overhead are not considered, then the execution times of W on a single processor and on an infinite number of processors are computed by

$$T(1) = \sum_{i=1}^{m} t_i(1) = \sum_{i=1}^{m} \frac{W_i}{\Delta}$$

$$T(\infty) = \sum_{i=1}^{m} t_i(\infty) = \sum_{i=1}^{m} \frac{W_i}{\Delta}$$

The asymptotic speedup is formally defined as

$$S_{\infty} = \frac{T(1)}{T(\infty)} = \frac{\sum_{i=1}^{m} W_i / \Delta}{\sum_{i=1}^{m} W_i / i \Delta} = \frac{\sum_{i=1}^{m} W_i}{\sum_{i=1}^{m} W_i / i}$$

This speedup is equivalent to the average parallelism A given above. Note that  $S_{\infty}$  is obtained under the assumption of having an infinite number of available processors and no communication latency. Thus the asymptotic speedup is the best possible speedup that can be achieved.

# 3.2 Three Speedup Modes

In this section, we consider three well-known speedup models. They are fixed-size, fixed-time, and memory-bounded speedup models.

**Fixed-size Speedup** In the asymptotic speedup model, we assume that the number of available processors is unbounded. If the number of processor n is taken into account, and n < i, then

$$t_i(n) = \frac{W_i}{i\Delta} \left[ \frac{i}{n} \right]$$

Note that this equation still hold for  $n \ge i$ , in which case,  $\lceil i/n \rceil = 1$ . Hence,

$$T(n) = \sum_{i=1}^{m} \frac{W_i}{i\Delta} \left[ \frac{i}{n} \right]$$

and the speedup is

$$S(n) = \frac{T(1)}{T(n)} = \frac{\sum_{i=1}^{m} W_i}{\sum_{i=1}^{m} \frac{W_i}{i} \left[ \frac{i}{n} \right]}$$

If communication latency and other system overhead are considered, the speedup becomes

$$S(n) = \frac{\sum_{i=1}^{m} W_i}{\sum_{i=1}^{m} \frac{W_i}{i} \left\lceil \frac{i}{n} \right\rceil + Q(n)}$$

where Q(n) is the sum of all the overheads. Usually, it is different to derive a closed form for Q(n) for it depends not only on the machine but also on the application and the problem allocation. In the later discussions, we assumed Q(n) = 0.

If we assume that the problem size, or workload, is fixed, and the workload only contains two parts, a sequential part (DOP = 1), and a perfectly parallel part (DOP = n), i.e.,  $W_i = 0$  for 1 < i < n in the parallelism profile, then the speedup becomes

$$S(n) = \frac{W_1 + W_n}{W_i + W_n/n}$$

Let  $\alpha$  be  $W_1/(W_1+W_n)$ , representing the percentage of the sequential portion. If the workload is normalized to 1, i.e.,  $W_1+W_n=1$ , then  $W_1=\alpha$ , and  $W_n=1-\alpha$ . The speedup is

$$S(n) = \frac{1}{\alpha + (1 - \alpha)/n} = \frac{n}{1 + (n - 1)\alpha}$$

This is known as Amdahl's law. In 1967, Amdahl [Amdahl67] made the observation that if  $\alpha$  is the sequential fraction in an algorithm, then no matter how many processors are used, the speedup is upper bounded by  $1/\alpha$ .  $\alpha$  is called *sequential bottleneck*.

Two observations can be made from the speedup formulation. If  $\alpha = 1$ , S(n) = 1, i.e., no part can be parallelized. If  $\alpha = 0$ , S(n) = n, i.e., the given algorithm can perfectly be parallelized, thus obtaining the maximum speedup.

For a variety of parallel systems with any number of processors n, speedup close to n can be achieved by simply running the parallel algorithm on large enough problems. Much work has been done on that (see for example [Kumar87; Lee87]).

**Fixed-time Speedup** To study how small the turnaround time of a problem could be, Amdahl fixes the problem size, thus leading to the development of the fixed-size speedup, which is suitable for algorithms in which the problem size cannot be scaled. However, there exist many problems whose execution time is not so critical (although they may have time limitations). Instead, we emphasize their accuracy. When the machine size is increased and more computing power obtained, we may increase the problem size and perform more operations, thus obtaining more accurate solution, yet keeping the turnaround time unchanged. This observation lead Gustafson to develop the fixed-time speedup model.

Let W' be the total amount of scaled work,  $W_i'$  be the amount of scaled work with DOP = i, and m' be the maximum DOP of the scaled problem. We have  $W = \sum_{i=1}^{m'} W_i'$ . In order to keep the same turnaround time of the scaled problem as the sequential version (before scaled), T(1) = T'(n) must be satisfied, that is

$$\sum_{i=1}^{m} W_{i} = \sum_{i=1}^{m'} \frac{W'_{i}}{i} \left[ \frac{i}{n} \right] + Q(n)$$

(x)

Thus the fixed-time speedup is

$$S'(n) = \frac{T'(1)}{T'(n)} = \frac{\sum_{i=1}^{m'} W_i'}{\sum_{i=1}^{m'} \frac{W_i'}{i} \left\lceil \frac{i}{n} \right\rceil + Q(n)} = \frac{\sum_{i=1}^{m'} W_i'}{\sum_{i=1}^{m} W_i}$$

(xx)

As with the fixed-size speedup, we assume the work only contains a sequential part and a perfectly parallel part. And we also assume the sequential part is independent of the problem size or system size, i.e.,  $W_1 = W_1'$ . From Eq. (x), we have  $W_1 + W_n = W_1' + W_n'/n$ , thus  $W_n' = nW_n$ . The speedup becomes

$$S'(n) = \frac{W_i' + W_n'}{W_i + W_n} = \frac{W_1 + nW_n}{W_1 + W_n}$$

Let  $\alpha = W_1$  and  $1 - \alpha = W_n$ , we rewrite S'(n) as

$$S'(n) = n + (1 - n)\alpha$$

This fixed-time speedup is known as Gustafson's scaled speedup [Gustafson88]. To keep the turnaround time unchanged, we have  $W'_n = nW_n$ . This means that the parallel part scales up linearly with the system size. Hence, Gustafson's law supports scaled performance.

In Amdahl's model, the load on each processor decreases as the number of processors increases, and finally the sequential part dominates the performance and the speedup is bounded by  $1/\alpha$ . In Gustafson's model, however, when the number of processors increases, the parallel part of the workload scales up linearly  $(W'_n = nW_n)$ . Thus the sequential part is no longer a bottleneck. That is why Gustafson's law offers a good speedup. Two figures in Gustafson's original paper [Gustafson88] explain that clearly.

Some experiments were done at Sandia by Gustafson, Montry and Benner [Gustafson88a; Benner88], and near-linear speedup was obtained on a very large parallel system. On a 1024-processor hypercube

architecture, three high speedups: 1021, 1020, and 1016 were achieved for three practical applications.

One disadvantage of the fixed-time model is that not arbitrarily large number of processors can effectively be used to keep the turnaround time unchanged. Worley [Worley90] found that in order to keep the turnaround time fixed, no more than 50 processors can effectively be used for many common scientific problems. For some other problems, however, he found that near-linear time-constrained speedup can be obtained, which means that arbitrarily large instances of the problems can be solved within a fixed period of time by simply increasing processors. Gupta and Kumar [Gupta93] classify parallel systems which yield linear and sublinear time-constrained speedup curves.

**Memory-Bounded Speedup** Sun and Ni [Sun93] notice that in parallel systems the scaled problem size is limited by memory space. Under the assumption of distributed shared memory multicomputer systems, they develop the memory-bounded speedup.

The requirement of an algorithm consist of two parts. One is the memory requirement (M), and the other is the computation requirement or workload (W). For a given algorithm, these two are related to each other, i.e., W = g(M) or  $M = g^{-1}(W)$ .

In distributed shared memory systems, the local memory capacity is fixed, but the total available memory increases linearly with the number of processors available. We write  $W = \sum_{i=1}^{m} W_i$  as the workload for sequential execution on a single processor, and  $W^* = \sum_{i=1}^{m^*} W_i^*$  as the scaled workload for execution on n processors. The following condition must be satisfied:

$$W^* = g(nM) = g(n g^{-1}(W))$$

The memory requirement for any active processor is thus bounded by  $g^{-1}(\sum_{i=1}^m W_i)$ . Like Eq. (xx), we have

$$S^{*}(n) = \frac{\sum_{i=1}^{m^{*}} W_{i}^{*}}{\sum_{i=1}^{m^{*}} \frac{W_{i}^{*}}{i} \left[ \frac{i}{n} \right] + Q^{*}(n)}$$

If we assume g is a semihomomorphism, i.e., g(nM) = G(n)g(M), then the scaled parallel part is

$$W_n^* = g(nM) = G(n)W_n$$

Under the same assumption as is made with the fixed-time model, we can get the memory-bounded speedup as follows

$$S^*(n) = \frac{W_1^* + W_n^*}{W_1^* + W_n^*/n} = \frac{W_1 + G(n)W_n}{W_1 + G(n)W_n/n}$$

This memory-bounded speedup is actually a general speedup model. Note that

- If G(n) = 1, it becomes equivalent to Amdahl's law;

- If G(n) = n, it becomes equivalent to Gustafson's law;

- If G(n) > n, the computational workload grows faster than the memory requirement, and execution time is likely to be the scalable constraint. Thus, the memory-bounded model will likely offer a higher speedup than the fixed-time model does;

- If G(n) < n, the memory capacity is likely to be the scalable constraint when n is large. Thus the fixed-time speedup is likely better.

[Sun93] give an example on how to find G(n) for an matrix multiplication algorithm. For Sun's other papers that address scaled speedup issues, interested readers are referred to [Sun90; Sun91].

In addition to the three famous speedup models described above, there still exist many other definitions of speedup, such as *generalized speedup*, *cost-related speedup*, *superlinear speedup*, and so on. They approach the problem in different ways. Some of them can be found in [Barton89; Gustafson91; Helmbold90; Sun91].

## 3.3 Isoefficiency Function

The isoefficiency concept was first introduced by Kumar and Rao [Kumar87]. It is especially useful in analyzing scalability of parallel algorithm-architecture combinations.

Let  $T_1$  be the sequential execution time,  $T_P$  be the parallel execution time on p processors, and  $T_O$  be the total overhead (including idling, communication, and contention over shared data structures). We can see that

$$T_P = \frac{T_1 + T_O}{p}$$

The speedup is

$$S = \frac{T_1}{T_R} = \frac{pT_1}{T_1 + T_0}$$

The efficiency is then computed by

$$E = \frac{S}{p} = \frac{T_1}{T_1 + T_O} = \frac{1}{1 + T_O/T_1}$$

Let W be the workload or problem size, which could be measured by the number of operations the best sequential algorithm executes to solve the problem on a single processor, and  $t_c$  be the cost of each operation. Then  $T_1 = t_c W$ . The efficiency can be rewritten as

$$E = \frac{1}{1 + T_O/t_c W} \tag{x}$$

The isoefficiency concept is based on the following observations. First, if the problem size (W) is fixed, the efficiency decreases as p increases because  $T_O$  increases with p. Second, if p is fixed, then the efficiency increases with the problem size because the overhead  $T_O$  grows slower than W for a given p. Thus it is possible to maintain a constant efficiency E (0 < E < 1) by increasing the problem size W proportionally with increasing the machine size.

Eq. (x) can be rewritten as

$$W = \frac{1}{t_o} \left( \frac{E}{1 - E} \right) T_o = K T_o$$

where  $K = E/(t_c(1-E))$ , which is a constant for a given E. If the problem size needs to grow as fast as  $f_E(p)$  to maintain an efficiency E, then  $f_E(p)$  is defined to be the isoefficiency function of the algorithm-architecture combination for efficiency E, i.e.,  $f_E(p) = KT_O$ . Different isoefficiency functions for different parallel systems can be found in the table of [Kumar87].

Isoefficiency is powerful in scalability analysis. A small isoefficiency function implies that small increments of the problem size are sufficient for effectively utilizing an increasing number of processors, and hence the parallel system is highly scalable. Conversely, a large isoefficiency function implies that the system is poorly scalable. For example, [Kumar87] shows that the parallel algorithm for solving the 0/1 knapsack problem given in [Lee87] is highly scalable for its isoefficiency function is  $O(N \log N)$ , while a frequently used parallel formulation of quicksort [Quinn87] has an exponential isoefficiency function, thus it is poorly scalable.

[Gupta91] presents scalability analysis of four different algorithms, which shows isoefficiency function is a proper metric for scalability analysis. For a detailed description of the isoefficiency concept and its applications, the following papers are recommended: [Grama93] and [Gupta93a].

## 3.4 Scalability Analysis

Scalability analysis plays an important role in performance evaluation of large parallel systems. On large

systems, one key issue is how to effectively utilize the processors provided by the system. Usually as more processors are used, the efficiency, utilization, and speedup etc. will drop. Scalability is such a metric that measures the capacity to effectively utilize an increasing number of processors.

A simple definition of scalability is that the performance of a parallel architecture increases linearly with respect to the number of processors used for a given algorithm. This definition involves two factors: architecture and algorithm, neither of which can be ignored. In fact, scalability studies determine the degree of matching between a computer architecture and an application algorithm. For different algorithm-architecture combinations, the scalability analysis may end up with different conclusions. An architecture may be scalable for one algorithm, but may not at all for another [Hwang93].

In the literature, lots of work on scalability analysis can be found. Kumar and Gupta [Kumar94] summarize the following situations where scalability analysis is found to be very useful.

- Selecting the best algorithm-architecture combination for a problem under different constraints on the growth of the problem size (workload) and the number of processors (machine size);

- Predicting the performance of a parallel algorithm and a parallel architecture for a large number of processors from the known performance on fewer processors;

- For a fixed problem size, determining the optimal number of processors to be used and the maximum speedup that can be achieved;

- Predicting the impact of changing hardware technology on the performance and thus help design better parallel architectures for solving various problems.

The notion of scalability is closely related to the notions of speedup and efficiency. To maintain the speedup and efficiency at a reasonable level, we have to increase the workload (*W*) properly with increasing the machine size (*n*). In different situations, the workload needs to be increased at different rates with respect to the number of processors. In some situations, if the workload needs to grow linearly w.r.t. *n* (which implies linear scalability in problem size), we say that the parallel system is highly scalable. On the other hand, if we need an exponential growth in the workload w.r.t. the machine size, then we say that the parallel system is poorly scalable, because to keep a constant efficiency or a good speedup, the increase in the problem size must be explosive, which is always limited by the memory capacity, and impossible in practice [Kumar87].

Gustafson's law, discussed earlier, supports the scaled speedup, which is obtained when the problem size grows linearly with the machine size  $(W_n' = nW_n)$ . If the speedup curve is linear or near-linear with respect to the machine size, then the parallel system is considered to be scalable. Carmona and Rice [Carmona89; Carmona91] give detailed explanations for Amdahl's law and Gustafson's law. They provide new and improved interpretations of the serial and parallel fraction parameters commonly used in the literature. The interpretations are based on quantifiable expressions of these fractions. The authors also give new definitions of speedup and efficiency and introduce a general model of parallel performance.

The isoefficiency function is also a proper metric for analyzing scalability. An important feature of isoefficiency analysis is that in a single expression, it succinctly captures the effects of characteristics of a parallel algorithm as well as the parallel architecture on which it is implemented. As stated earlier,  $W = f_E(p) = KT_O$ , where  $f_E(p)$  is the isoefficiency function. If  $f_E(p)$  is small, then only small increments are required to effectively utilize an increasing number of processors. Thus the parallel system is considered to be highly scalable. In Kumar and Rao's framework, if an isoefficiency function exists, then the parallel system is considered to be scalable; otherwise it is unscalable. However, for some problems, the function would probably be very large. This means that the workload must be increased very fast w.r.t. the machine size. But in practice the problem size is bounded by memory capacity. Thus, from a practical viewpoint such systems should also be considered unscalable (even though their isoefficiency functions exist).

Nussbaum and Agarwal [Nussbaum91] give their definition for scalability. "For a given algorithm, an architecture's scalability is the ratio of the algorithm's asymptotic speedup when run on the architecture in

question to its corresponding asymptotic speedup when run on an EREW PRAM, as a function of problem size." The asymptotic speedups for the ideal machine (EREW PRAM) and for the given architecture are

$$S_I(s,n) = T(s,1)/T_I(s,n)$$

and

$$S(s,n) = T(s,1)/T(s,n)$$

respectively. Thus the scalability is

$$\Psi(s,n) = \frac{S(s,n)}{S_I(s,n)} = \frac{T_I(s,n)}{T(s,n)}$$

where s is the problem size and n is the number of processors. Intuitively, the larger the scalability, the better the performance that the given architecture can yield running the given algorithm. This definition captures not only algorithm scalability (measured through the asymptotic speedup on an ideal machine), but architecture scalability as well. Note that, in the ideal case,  $S_I(s,n) = n$ , we have

$$\Psi(s,n) = \frac{S(s,n)}{n} = E(s,n)$$

This means that  $\Psi(s,n)$  is a better metric for scalability than the efficiency E(s,n) is. The reason is that the asymptotic speedup measures the parallelism inherent to the algorithm (refer to section 3.1). This definition is useful in comparing different architectures for a given algorithm. It is, however, useless in comparing different algorithm-architecture pairs for solving the same problem.

Karp and Flatt [Karp90] use serial fraction f as a metric for measuring the performance of a parallel system on a fix-sized problem. They define

$$f = \frac{1/S - 1/n}{1 - 1/n}$$

where S is the speedup, and n is the number of processors. Interestingly, if we rewrite this equation as

$$S = \frac{n}{1 + (n-1)f}$$

It becomes Amdahl's law, and f is just the serial fraction  $\alpha$ . In general, a smaller f is desirable. If f increases with n, it is considered as an indicator of rising communication overhead, and thus an indicator of poor scalability. The authors explain the phenomenon that f decreases with increasing n as an anomaly caused by superlinear speedup effects or cache effects.

Zorbas *et al.* [Zorbas89] introduce the concept of an overhead function  $\Phi(n)$ . If the execution time T(n) is given by

$$T(n) \le t_c (W_1 + W_n/n) \times \Phi(n)$$

then the smallest function  $\Phi(n)$  that satisfies this equation is called the overhead function and is computed by

$$\frac{T(n)}{t_c(W_1 + W_n/n)}$$

In general, the overhead grows with the number of processors. Thus the rate at which  $\Phi(n)$  grows reflects the degree of scalability. The smaller the rate, the more scalable the parallel system. And in the ideal case where  $\Phi(n)$  remains fixed, the parallel system is ideally scalable.

Something like Nussbaum and Agarwal's method [Nussbaum91], where they compare the performance of a parallel system with that of the ideal machine, Van-Catledg [Van-Catledg89] compare the performance of a parallel system with that of a supercomputer (called reference machine) for the same problem. Let W be the problem size measured by the number of operations, and s be the serial fraction. Then the number of sequential and parallel operations equals sW and (1-s)W; and they become G(k)sW and F(k)(1-s)W after the problem size W is scaled up by a factor k. Thus, the parallel execution time on the parallel system

with *n* processors is given by

$$T(n) = t_c W \left( G(k)s + \frac{F(k)(1-s)}{n} \right)$$

Similarly, the execution time on the reference machine with n' processors is

$$T'(n') = t_c'W\left(G(k)s + \frac{F(k)(1-s)}{n'}\right)$$

The relative performance is defined as T(n)/T'(n'). If for some n the relative performance is 1, then n is used as equal performance condition to measure the scalability of the parallel system. The parallel system is considered more scalable with a smaller n. The author also shows, by examples, that a system with fewer faster processors is better than a system with more but slower processors. This is intuitively true because a system with more processors incurs more overheads and the probability that more processors are idle is higher.

In addition to those discussed above, there are still some useful concepts, such as *shape*, *execution profile*, *phases*, etc., which are more related to workload characterization, and will be described in the next section.

## 4 Workload and Workload Characterization

Any system is designed to be used in a specific environment with a specific workload. Therefore, the performance analysis of a system must be carried out with a certain workload under which the system is designed to run. Consequently, selecting proper workloads is important in performance evaluation. Workload is defined as the entity of all individual tasks, transactions, and data to be processed in a given period of time, or simply, the workload of a computer system is the user's demand from the system [Oed81]. A real workload is often very complex and unrepeatable, so it cannot be used properly for studies. Because of this, a test workload model must be designed. This model must have the following characteristics.

- It must be a representation of the real workload. That is the static and dynamic behavior of the real workload must be accurately captured. In other words, the test workload model must perform the same functions in the same proportions as the real workload, and it must demand the same system's resources in the same proportions and rates as the real workload;

- It must be easily reproduced and modified, such that the workload can be used repeatedly in different studies;

- It must be compact, such that the workload can be easily ported to different systems. This is quite useful in comparing different systems for the same purpose.

In this section, we first present several types of workloads that are traditionally used, and then review some techniques that are now commonly used in workload characterization.

#### 4.1 Workload

**Instruction Mix** *Instruction mix* specifies the relative frequencies of different types of instructions. The types of instructions and their relative frequencies used in an instruction mix must be the same as those used in the real workload. Then the average execution time can be measured on the system to be tested. The Gibson mix [Gibson70] developed for use with IBM systems is perhaps the most widely known in industry. The instruction level of the mixes can be extended to statement level of high-level languages, called *statement mix*.

One of the advantages of an instruction mix is that it is relatively easy to design and use. However, it has several disadvantages. Because it is designed to measure the speed of CPU, it is not suitable for evaluating the whole system's performance if the CPU is not the bottleneck. Furthermore, it cannot be properly used to compare two CPUs with different instruction sets (e.g., RISC and CISC). Because modern

computer systems often adopt new technologies, such as cache, pipeline, in pre-fetching instructions to get high efficiency, the problems are difficult to tackle properly with instruction mixes. Because of this, this technique becomes obsolete. Some early papers are available to the interested readers: [Knuth71], [ISE79], and [Febish81].

**Synthetic Programs** Synthetic programs are also called synthetic benchmarks which are programs designed to simulate real workload. They do no "useful" work, but consume amounts of system resources or request amounts of system services. The main advantages are that they can be quickly developed and easily modified to simulate a wide spectrum of real problems through a set of control parameters and they do not necessarily use real data files. The disadvantage of synthetic programs is that they are often too simple to accurately reflect some real system issues, such as disk caches.

Shein *et al.* [Shein89] proposed a synthetic program, named NFSStone, to measure the performance of SUN's NFS (Network File System) [Sandberg85]. It uses a single client that issues various requests for file operations in order to stress and measure the performance of the server. However, using only one client is not sufficient to stress the server. Another problem with the NFSStone is that the file and block sizes does not properly reflect the real workload, which may influence the accuracy.

Park and Becker [Park90] developed an I/O benchmark called IOStone. It performs data read and write on 400 files, the total size of which is 1 MB. The output of the program is throughput which is measured by IOStone/second. One problem with IOStone is that no I/O parallelism is introduced.

Noticing that most scientific applications often deal with large amount of data, Chen and Patterson [Chen93] describe a scientific benchmark which operates on very large files (100 MB) in large units (128 KB). Results from two sample scientific workloads are presented, but no other details are introduced in that paper.

**Application Benchmarks** Many computer systems are designed to be used in particular applications, such as airline reservations or transaction processing. To evaluate the performance of such systems or to compare them, the synthetic benchmarks are not sufficient. This demand gives rise to application benchmarks, which incorporate a set of representative functions the applications might use. Unlike a synthetic benchmark, an application benchmark is intended to do some real work as is done by standard programs, such as banking systems, editors, compilers, etc..

Since the 70', Debit-Credit benchmarks have become more and more popular. These application benchmarks are designed to compare transaction processing systems. The commonly used metric is price-performance ratio. The price includes the total cost to purchase, install, and maintain the system (both hardware and software) over a specified period of time. The performance is measured by throughput in terms of TPS (transactions per second). Each transaction may involve a database search, query answering, and database update operations. The database system used typically includes such records as account, teller, branch, and so on. Banking or business systems should be designed to deliver high TPS rates. The first benchmarks of this kind is known as TP1, which was originally proposed in 1985 [Anonymous85], and has already become the *de facto* standard for gauging transaction processing systems and rational database systems.

To define transaction processing benchmarks more precisely, the Transactions Processing Performance Council (TPC) was formed in August 1988 and proposed its first benchmark, TPC-A, in 1989 [TPC89]. This benchmark is actually based on TP1, and the throughput is measured in terms of TPS such that 90% of all transactions provide 2 seconds or less response time. TPC-A requires that all the requests be from the real terminals, and the average interarrival time of the requests is 10 seconds. A new version of the benchmark, named TPC-B, is later proposed [TPC90]. Like its previous versions, TPC-B uses a database containing records for accounts, tellers, and branches. It simulates typical account changes on the database by carrying out Debit-Credit transactions. The throughput is also measured in the same way as TPC-A. The price for the system and required storage, and a graph of throughput are reported at the end of test. Unlike TPC-A, the requests of which are from the real terminals, TPC-B generates requests using internal drivers,

which can generate the requests as fast as possible.

**Some well-known benchmarks** When it comes to the workload, we cannot ignore several well-known benchmarks, which are still commonly used in industry although they are rather old. Below, we briefly review some of them. The interested readers are referred to the literature for more details.

Whetstone is actually a synthetic benchmark [Hwang93]. It includes both integer and floating-point operations involving array addressing, subroutine calls, parameter passing, fixed/floating-point arithmetic, conditional branching, and trigonometric/transcendental functions. The operations are programmed according to the statistical data of about 1000 ALGOL programs. Because of this, it is considered to be a standard floating-point benchmark. The test results are measured in the number of *Kwhetstone/s* (Kilo Whetstone Instructions Per Second) that the system can perform. The main disadvantages of Whetstone benchmark are that it is compiler sensitive, and it is designed to test CPU performance: no I/O involved.

*Dhrystone* should also be considered a synthetic benchmark [Hwang93]. It is CPU-intensive, and designed to represent systems programming environment, thus no floating-point operations and I/O processing are exercised and the majority of the CPU time is spent in string manipulating. Since it was proposed, it has been updated for several times, and is considered to be a popular measure of the integer performance of modern processors [Jain91]. The results are measured in *Kdhrystones/s* (Dhrystone Instructions Per Second). The disadvantages found in Whetstone also apply to this benchmark.

The *LINPACK* benchmark was designed by Dongarra [Dongarra83]. It contains a number of programs that solve dense systems of linear equations using the LINPACK subroutine package. LINPACK is a general-purpose FORTRAN library of mathematical software for solving dense linear systems of equations of order 100 or higher. LINPACK benchmarks are compared based on the execution rate as measured in Mflops. In fact, many published Mflops and Gflops results are based on running the LINPACK code with prespecified compilers [Hwang93]. Many LINPACK benchmark results obtained by running on various computer systems can be found in [Dongarra92].

#### 4.2 Workload Characterization

#### 4.2.1 Overview

Workload characterization is the process of developing a workload model that can be used repeatedly. In order to design a workload model, it is essential to carefully study and understand the key characteristics and to know the limitations of the model. Oed and Mertens [Oed81] list and discuss in detail four basic levels, at which the performance of a computer system and the respective workload is influenced. They are *user*, *hardware*, *software*, and *organization*.

A workload model is a miniature workload with reduced information. The issues addressed in section 2.1 also apply to modeling workload. Often the amount of data collected (either by measuring or any other methods) is very large. Thus careful examination of classification of the data should be made to eliminate all the negligible parts and include only those that best describe the real workload.

In modeling workload, representativeness is one of the main characteristics that should be considered. The representativeness of a workload model can be determined by an equivalence relationship [Ferrari78]. Given a system S, a set of performance indices L can be obtained from a certain workload W. Formally, a function  $f_s$  can be defined for S, so that  $L = f_s(W)$ . If  $W_r$  is a real workload and  $L_r$  is the corresponding performance indices, then we have  $L_r = f_s(W_r)$ . Similarly, we have  $L_m = f_s(W_m)$ , where  $W_m$  is the workload model and  $L_m$  is the corresponding performance indices.  $W_m$  is considered to be equivalent to  $W_r$  if  $L_m$  falls within certain boundaries of  $L_r$ .

The methodologies and techniques applied for constructing workload models are highly related not only to the goals of the studies but to the system under study as well. The problems encountered in the workload characterization of centralized systems are well-known and have been approached and solved

quite a long time ago. However, similar conclusions cannot be drawn for more recent types of architectures, such as multiprocessor systems, client-server architectures, and so on [Calzarossa93]. In the parallel performance evaluation literature, we find it hard to summarize systematic ways for modeling workload. In the sequel we first review some general techniques that are commonly used in workload characterization for traditional system architectures. Some of them can also be useful to modern architectures. Then we survey some papers that address workload characterization for modern architectures.

It should be pointed out that workload characterization is related to other techniques of performance evaluation. The original data that are used are often obtained from measuring the system or from accounting routines of the system. However, the measured data cannot be directly used in performance studies without necessary processing. Actually, the techniques to be discussed below are used to process data. Workload characterization is also related to analytical modeling and simulation. For example, in [Pettey95], genetic algorithms (GAs) are used to accurately extract the assumed exponentially distributed customer class demands for a closed queueing network from the monitor data.

Before describing the techniques, we think it necessary to explain two terms that are commonly used in the workload characterization literature. They are *workload component* and *workload parameters*. Workload component (or workload unit) is often used to denote the entity that makes the service requests to the system under study. Examples of workload components are applications, programs, commands, machine instructions, and so on. Workload parameters (or workload features) mean the measured quantities, service requests, or resource demands, which are used to model or characterize the workload. Examples are transaction types, packet sizes, page reference pattern, and so on [Jain91].

#### 4.2.2 Steps of Workload Characterization

Ferrari [Ferrari83] groups the main operations to be performed in implementing workload models into three phases: *formulation phase*, *construction phase*, and *validation phase*, each of which involves several operations. They are summarized as follows.

In the formulation phase, decisions should be made on what parameters are to be selected. This is often influenced by two factors: objectives of the study and the availability of parameters. Among the first operations to be performed is the definition of the workload basic components. After studying the objectives and verifying their availability, the parameters to be used to characterize the workload basic components are selected on the basis of the modeling level of detail. Two different levels are defined: the physical resource level and the functional level. If the model is constructed at the physical resource level, parameters, such as CPU time, memory space demand, number of I/O operations, etc., can be used. If the model is to be implemented at the functional level, the parameters that could be used are, for example, the number of compilations, and the number of executions of certain systems programs, and so on. Another issue that should be considered during this phase is the choice of the number of parameters to be used and the homogeneity of their values. This is very important in later statistical analysis, because they both will affect the degree of difficulty and accuracy of the resulting workload model.

In the construction phase, there are four fundamental operations. They are

- (1) The analysis of parameters;

- (2) The extraction of representative values;

- (3) Their assignment to the components of the model;

- (4) The reconstruction of the mixes of significant components;

During this phase, the main operation is using appropriate techniques to analyze the parameters. The workload may be considered as a set of vectors in an n-dimensional space, where n is equal to the number of the workload parameters. Each set of the parameter values is a point in the space. In order to reduce the number of points characterizing the workload, and identify groups of components with similar characteristics, a number of statistical techniques, which will be reviewed later in this section, can be

applied.

In the validation phase, the evaluation criteria for the representativeness of a model must be applied to establish the validity of the implemented model. The criteria should be determined according to the objectives of the study.

From the above description, we can see that the main considerations and the operations that an analyst should perform to build a workload model are almost the same as given in section 2.1. The readers can also find a similar summary in [Calzarossa93].

## 4.2.3 Workload Characterization Techniques

There exist many techniques (statistical methods) that have been successfully used in workload characterization. Again, there are many papers and books that address these techniques (see for example [Hartigan75; Oed81; Ferrari83; Jain91]). Summarized below are the most commonly used techniques. They are:

- Averaging

- Distribution Analysis

- Principal component analysis

- Clustering

- Markov models

Averaging Perhaps the simplest methods to characterize a parameter is to use a single value to represent the data obtained from measuring. The most intuitive method is averaging. There are a number of averaging methods, for example, arithmetic mean, geometric mean, harmonic mean, and so on. These techniques should be used under different conditions. Sometimes, to make the results more accurate preprocessing should be performed. For example, the outliers (whose value is very different from the typical ones) should be removed before averaging. Although in some cases this method is very useful and effective (for it need only one value to character a workload parameter), it is not very effective, or even absolutely useless in some others. For example, averaging is not sufficient if the data to be processed show a large variability. Variability is commonly measured by variance, standard deviation, coefficient of variation (COV), etc.. In a network router example, where source and destination addresses are used as parameters, the average address has no meaning at all. In such case, the most frequent value, or the top-n values should be specified.

**Distribution analysis** Given a number of workload parameters and their corresponding measured data, distribution analysis can be applied. The analysis can be made to each parameter independently (*single-parameter* analysis), or to some combinations of several parameters dependently (*multiparameter* analysis). The latter is often called *compound distribution* analysis. A commonly used method in distribution analysis is histogram. In this method, the complete parameter range is divided into several smaller subranges called *buckets* (or *cells*). Then the frequencies of the data items that fall within each bucket are counted.

With this, the minimum, maximum, mean, median and standard deviation etc. can be estimated. They can be used to characterize the distribution, or the frequencies can be directly used to generate random numbers with a similar distribution to that of the real parameter. The inherent problem of single-parameter analysis is the loss of the correlation information among different parameters. For example, a job that requires long CPU time may also requires a large number of I/O operations.

If the result of the single-parameter analysis cannot properly reflect the characteristics of the real workload because of the significant correlation between the parameters, the multiparameter analysis should be used. In multiparameter analysis, if n parameters are selected, an n-dimensional space (or correspondingly an n-dimensional matrix) can be created. As with the single-parameter analysis, the space is divided into a finite number of cells. If the whole range of each axis is divided into L parts, then the total

number of cells is  $L^n$ . Each component of the workload falls into one of the cells.

A workload model can be constructed from the distribution. A case study of this method can be found in the earlier literature (e.g. [Sreenivasan74]). Very often the number of components can be reduced using certain techniques [Ferrari83]. Thus, a test workload model with fewer number of data can be built. In spite of this, the resulting workload model is still too detailed. This restricts the usefulness of the method. Another drawback of this method is that it is difficult to plot the joint distribution when n is greater than two.

**Principal component analysis** This is a technique that transforms a set of variables into a set of principal components characterized by linear dependence on the variables in the original set and by orthogonality among its own variables. Because of its size reduction capability, it is often used in workload characterization [Ferrari83]. The main operations are to find the eigenvalues and the corresponding eigenvectors of the correlation matrix of a given set of variables based on a given set of their values.

Let  $\{x_1, x_2, ..., x_n\}$  be a set of *n* parameters, and  $\{y_1, y_2, ..., y_n\}$  be a set of factors. Jain [Jain91] lists the following conditions that must be satisfied.

(1) The y's are linear combinations of x's:

$$y_i = \sum_{j=1}^n a_{ij} x_j$$

where  $a_{ij}$  is the loading of variable  $x_j$  on factor  $y_i$ .

(2) The y's form an orthogonal set, i.e., their inner product is zero:

$$\langle y_i, y_j \rangle = \sum_k a_{ik} a_{kj} = 0$$

This condition means that  $y_i$ 's are uncorrelated to each other.

(3) The y's form an ordered set such that  $y_1$  explains the highest percentage of the variance in resource demainds,  $y_2$  a lower percentage,  $y_3$  a still lower percentage, etc.. This order is useful, because according to the level of modeling detail, only the first few factors can be selected to classify the workload components.

There are many books that describe in detail this technique (see for example [Rummel70; Harman76]). Applications of this technique can be found in [Hunt71] and [Serazzi81; Serazzi85].

Clustering The aim of the statistical technique is to group the workload components into *classes* or *clusters* so as to make the differences between the members of the same class smaller than those between the members of different classes. The similarity is measured by a certain criterion. The criterion most commonly used are *Euclidean distance*, weighted *Euclidean distance*, and *Chi-square distance*. The concept between clustering and the compound distribution addressed above is similar. The difference is that clustering determines the cells by the workload components themselves rather than by previous division [Oed81].

After the workloads are classified, one member from each class may be selected to represent the class in later studies, or similar to the compound distribution, several representative components may be selected from each class, according to the size of the class (relative frequency). This way, the number of the workload components can greatly be reduced.

Everitt [Everitt74] described various clustering techniques. Also, various algorithms that can be applied to workload characterization can be found in [Hartigan75]. They fall into two classes: *hierarchical* and *nonhierarchical*. The minimum spanning tree method is one of the most widely used hierarchical algorithms, while the k-means method is one of the most widely used nonhierarchical algorithms. Numerous case studies of this technique can be found in the literature. See for example [Wight81; Calzarossa86].

Markov models Markov models have found wide applications in modeling stochastic processes. They are also very useful in workload characterization. Markov models treat the state transition of systems. If we assume that the next state of a system depends only on the current state, then we say that the system

follows a Markov model (memoryless property). The memoryless property of Markovian systems makes them relatively simple to analyze. Markov models are usually described by a *transition matrix*, the elements of which are the probabilities of the next state given the current state. Although none of systems in the real world exactly follows this model, it does provide a good approximation of the reality.

In workload characterization, we sometimes need not only the number of service requests of each type but their order as well. Markov models provide a powerful means to deal with this requirement. When using Markov models in workload characterization, the states of the system can be defined in various ways according to the objective of the study. For instance, in certain cases we may view the service requests as the system states, where the next request can be determined by the present request. In others, we may view the execution of components as the states. If the system is executing component *i*, then we say that the system in state *i*. An example can be found in [Haring83], where a Markov chain is constructed at the task level. The nine different states of the system that correspond to the software resources used by the run are identified. The states include seven software resources employed (e.g., FORTRAN compiler, Editing, etc.) and two fictitious states (BEGIN and END). In real applications, the transition probability matrix can be worked out from the measured data. In the test workload we can simulate the probabilities with the help of a random number generator.

Detailed introductions to Markov models can be found in many books (See e.g. [Kleinrock75]). The descriptions of the technique used in workload characterization are given in more detail in [Ferrari83; Jain91]. And an application example is presented in [Agrawala78].

# 4.2.4 Parallel Workload Characterization Techniques

In the previous subsections, we described the main operations one should perform to model a workload, and a number of techniques that are traditionally applied to workload characterization. In this subsection, we survey some relatively new work on workload characterization for parallel architectures. Although the traditional techniques reviewed earlier can also be used, they are sometimes not sufficient and new techniques should be introduced. In what follows, we limit ourselves to the work which uses the techniques not yet reviewed in the previous subsection.

Parallel algorithms can be characterized in many ways. One example is the parallelism profile (see section 3.1), which is also useful in workload characterization, and will further be discussed later in this subsection. *Task graphs* are usually used for representing data-driven computations. A task graph is a directed graph which consists of nodes and arcs. Each node represents a sequence of computations (tasks), while the arcs represent data dependencies. Formally, a directed graph G = (N, A) is defined as a finite nonempty set N of nodes and a collection A of ordered pairs of distinct nodes form N; each ordered pair of nodes in A is called a directed arc or simply arc. If (i, j) is a directed arc, then it is an outgoing arc from node i, and an incoming arc to node j [Bertsekas89].

From a task graph, Calzarossa and Serazzi [Calzarossa93] identify the following measures. They are *N*, *in-degree*, *out-degree*, *depth*, *maximum cut*, and *problem size*. Here *N* is the total number of nodes in the graph; the in-degree and out-degree are the average number of incoming arcs and outgoing arcs of all the nodes, respectively; the depth is the longest path between input and output nodes, which is directly related to the execution time of the algorithm; the maximum cut is the maximum number of arcs taken over all possible cuts, which reflects the maximum theoretical parallelism that can be obtained during the execution; and the problem size is a measure of the size of the data.

Task graphs for representing workload are widely used in the literature (see for example [Mak90]). [Calzarossa93] gives two examples to illustrate a workload characterization process, where two typical parallel algorithms are analyzed. One is the block decomposition matrix multiplication from [Fox88], and the other is the LU decomposition from [Lord83]. The asymmetric task graph of LU decomposition indicates a high probability the maximum number of processors (maximum cut) will be used only for a small fraction of the global execution time. A table shows all the values of the above measures for both of

the examples.