### Overview **Communication Support for Task-Based** Motivation **Runtime Reconfiguration in FPGAs** Model Definition System architecture Shannon Koh o Task model Implementation model COMP4211 Advanced Computer Architectures Seminar **Research Direction** 1 June 2005 Dynamism – Single Task **Motivation** Today's FPGA-based Embedded systems run FPGA Core hardware/software Image Processing Memory partitioned applications I/O Write Int Data Address Bus Bus Hardware modules sharing the Embedded reconfigurable **AVR Core** resource

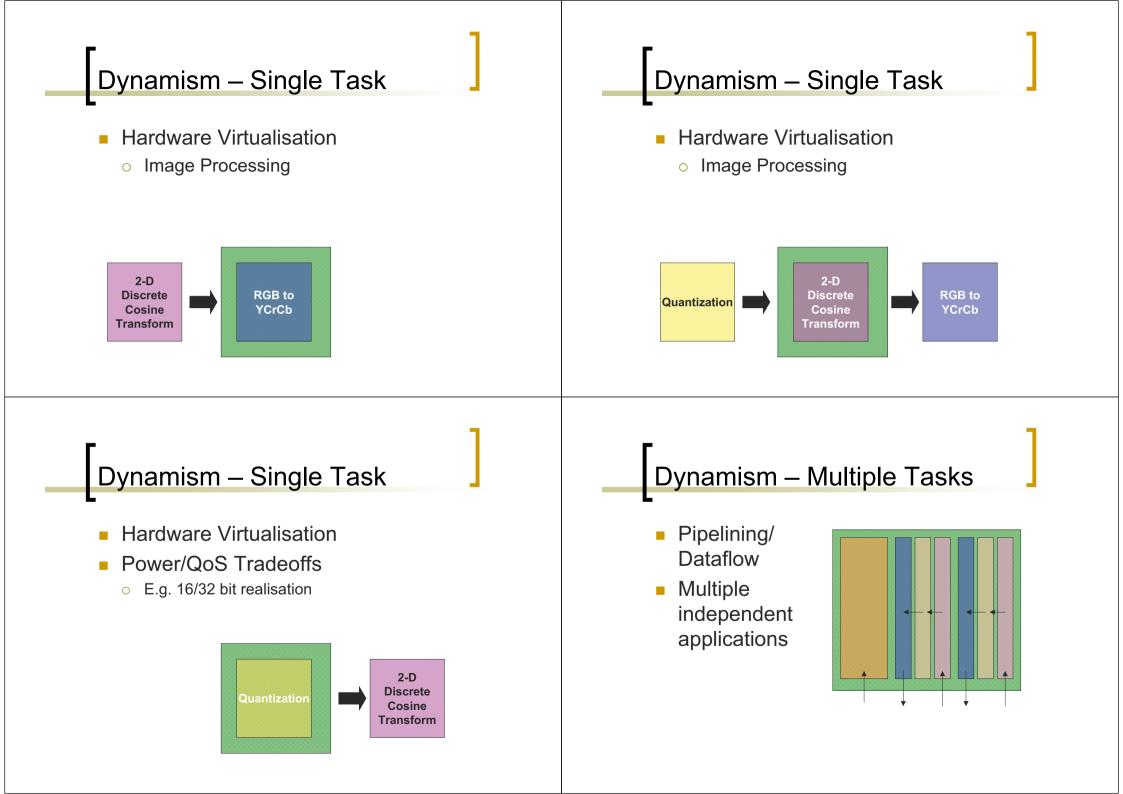

Conceivably have dynamism during runtime

Real Application: UAV Control System Hardware: Repetitious, long time-scale functions e.g. command pulse Software: Altitude and heading control

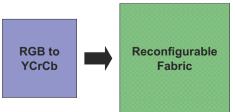

Hardware Virtualisation

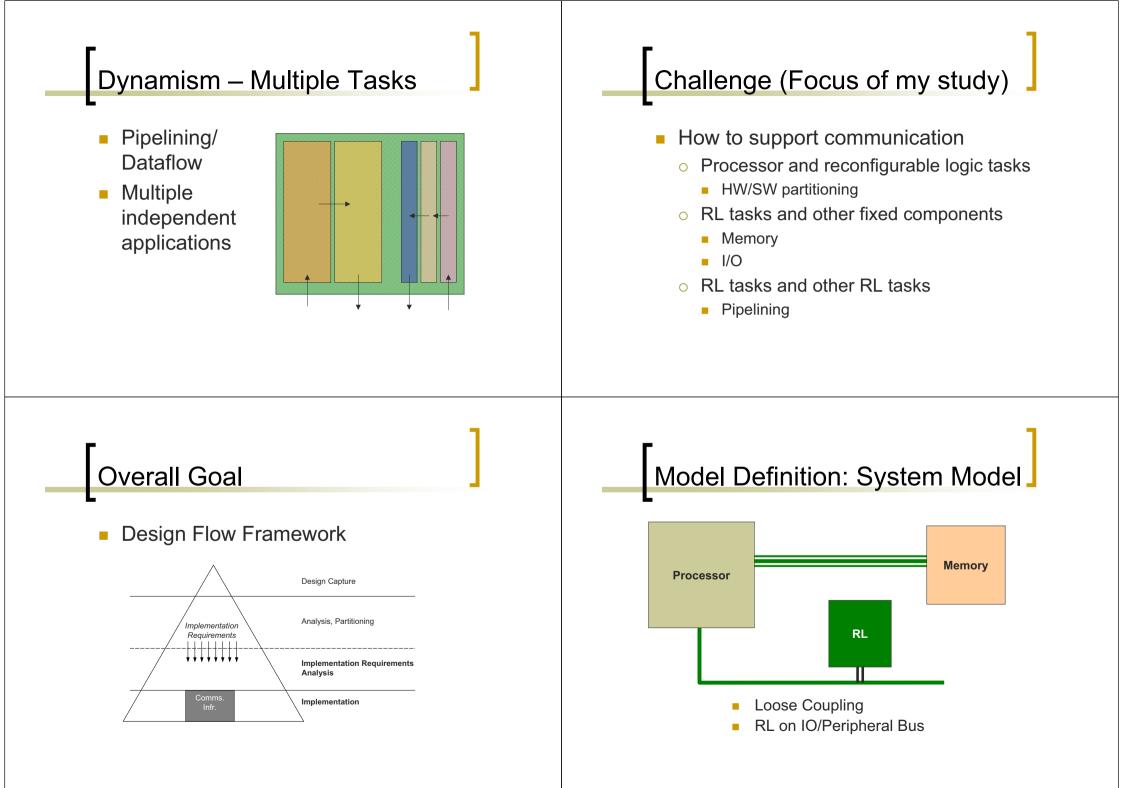

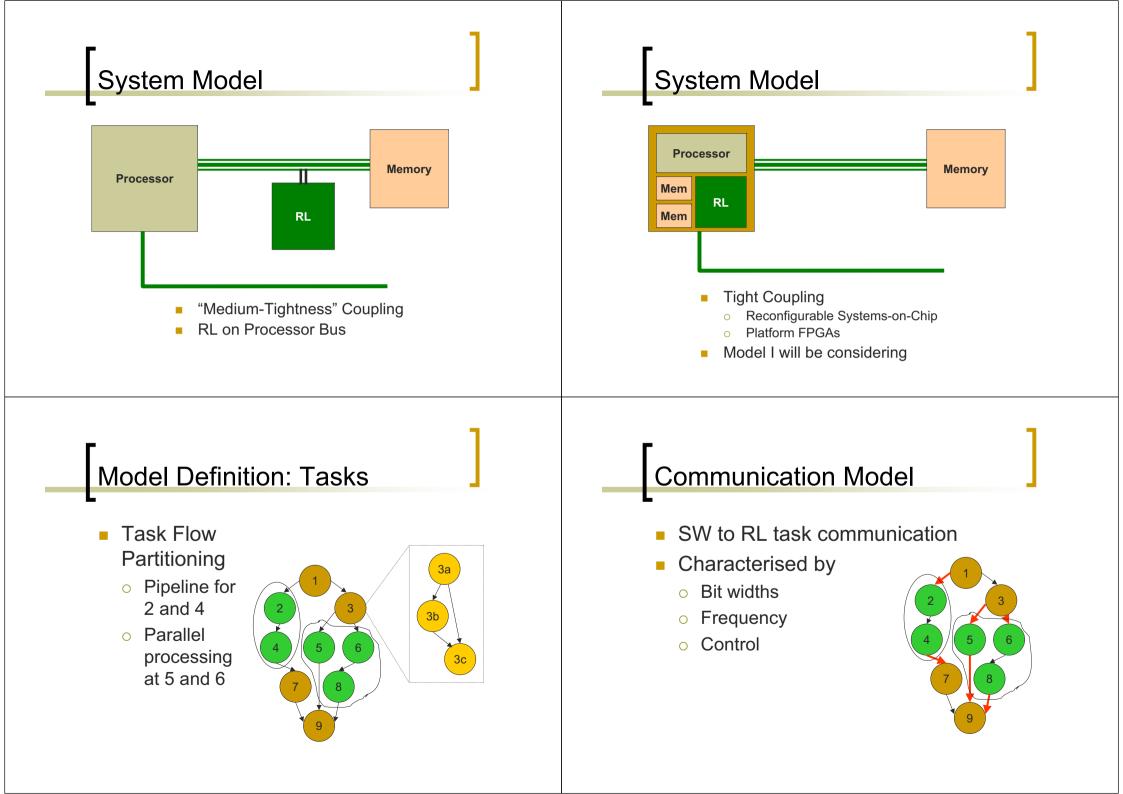

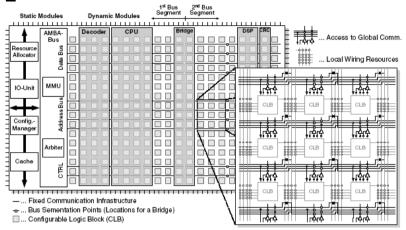

#### **Communication Model Implementation Model** Swappable Logic Units RI to RI task Advantages: Same characteristics SOA: Dedicated SLU routing apply? sLU Parallel Harness: Routing and • Have to cater for placement issues do possibility of task not not need to be considered being present later SLU Disavantages • SOA: Very difficult to **SL**U realise dynamic \$1.1 routing, fragmentation Parallel Harness: 0 (h) See with fine accel Less flexibility Xilinx Task-Based Network-on-Chip Reconfiguration Advantages: ossible I/Os Task wrappers and bus macros Commercially this block available model provide interfacing Realisable 0 Disavantages: Fixed IP1 0 No dynamic Logic sizing and Fixed PR PR Logic Logic placement Logic Off-Chip . . . Size and location IP1 IP2 IP3 in multiples of 4 Bus macros must be used No parallel IP2 IP3 Bus Macros communication Boundaries X290\_01\_03280 Block BAMs on same row [Kalte04] Recent Study: Min 1 (S), 6 (M), 55(L) Marescaux, T., Bartic, A., Verkest, D., Vernalde, S. and Lauwereins, R. (2002). Passthroughs . Large XCV2000E: 80 columns (max 20 possible Interconnection Networks Enabled Fine-Grain Dynamic Multi-tasking on FPGAs. required modules, about half are bus macros) In proceedings of the 2002 International Conference on Field-Programmable Logic.

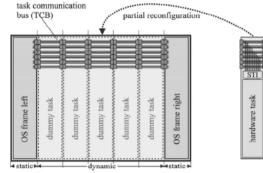

# 1 Dimensional Task Model

Kalte, H., Porrmann, M. and Rückert, U. (2004). **System-on-Programmable-Chip Approach Enabling Online Fine-Grained 1D-Placement.** In proceedings of the 11<sup>th</sup> Reconfigurable Architectures Workshop 2004.

### **Research Focus**

- Embedded systems

- SoC with reconfigurable logic

- Applications (Partitions & Schedules)

- o Multiple hardware modules

- o Run-time dynamism

- Specific Applications

- Optical flow algorithm

- o JPEG

## Hardware Operating Systems

Fixed-size pages, an example of parallel wiring harness

Steiger, C., Walder, H., and Platzner, M. (2004). **Operating Systems for Reconfigurable Embedded Platforms: Online Scheduling of Real-Time Tasks.** IEEE Transactions on Computers, Vol. 53, No. 11, November 2004.

## Problem to solve:

Given a partition and (dynamic) schedule, with known flows between components, how do we satisfy the communication requirements?

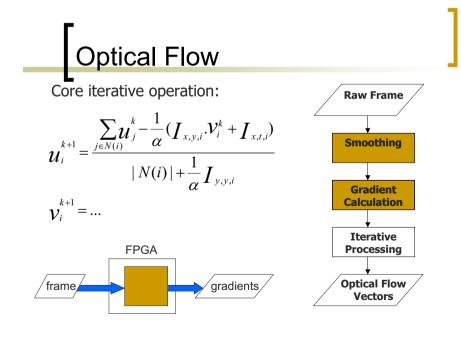

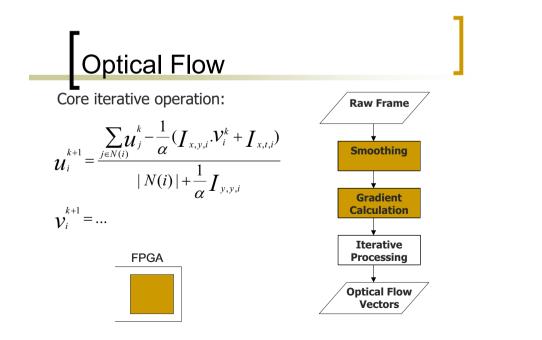

# Optical Flow

Determines velocity of pixels from frame to frame

• Closer objects have higher relative velocity

## System architecture

- Camera

567x378 @

- 567x378 @ 27.4 fps

- Framegrabber

- Motherboard

- P4-M 2.6GHz

- o 1024MB DDR 266

- BenNUEY board

- VirtexII XC2V6000

# **Requirements Analysis**

- Other Inputs e.g. device size

- Number of communication lines per module

- o Time allowed per module

- Implementation Plan

- Scheduling rules (not explicit schedule)

- Communication modules

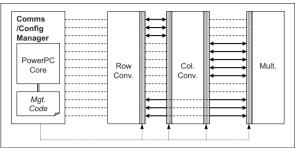

# Implementation

Virtex-II Pro/Virtex-4 FX

# Further Work

- Formal Definitions

- More Applications

- Dynamic Framework