# From Sequences of Dependent Instructions to Functions

An Approach for Improving Performance without ILP or Speculation

Ben Rudzyn

#### Disclaimer

The approach presented here comes from a paper of the same title. Written by Sami Yehia and Oliver Temam of Paris XI University. Presented at the 31<sup>st</sup> Annual International Symposium on Computer Architecture (ISCA'04)

While this presentation is my own work, the methodologies, experimental results, and graphs come from this paper.

#### Outline

- Background

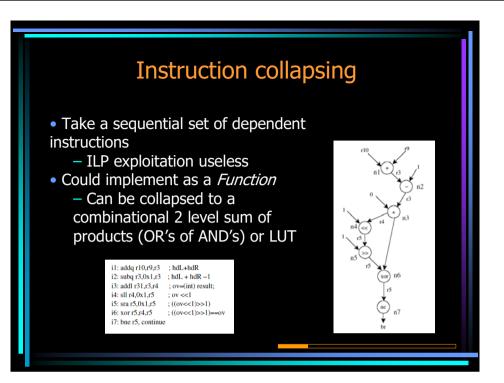

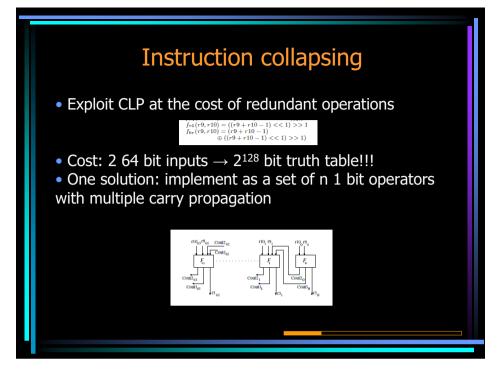

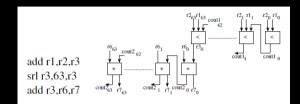

- Instruction collapsing

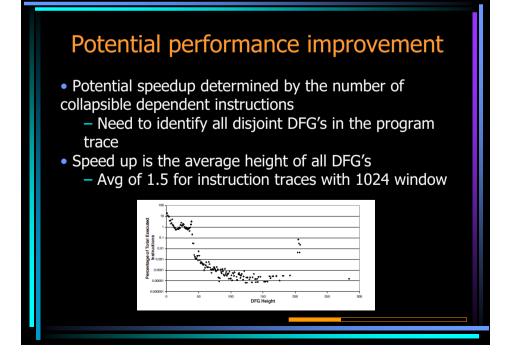

- Potential performance improvements

- Limitations of the approach

- Implementation

- Improvements to the approach

- Summary

#### **Background**

- Current processor trends are heavily reliant on pipelining and ILP exploitation

- On chip space devoted to these techniques, rather than to physical computing resources (ie FU's)

- Better improvements rely on software and hardware co-exploitation, but STILL look at ILP

- Propose a new approach that exploits circuit level parallelism, rather than instruction level parallelism

#### Limitations of the approach

- Number of physical inputs (register + carries)

- Hardware operator size fixed

- Load instructions

- Cannot be combined with dependent instructions

- Still semi collapsible

- Avg 24.4% of instructions

- Non collapsible instructions

- Eg syscalls, FP divide

- Avg 15% of instructions

- Result: only consider integer add/sub, constant shift, bit operations/manipulations and conditional branches

#### Limitations of the approach

Significant bit carries

- Height limitation

- Consider only those DFG's with height greater than the Function unit latency

- Allows better utilisation of all FU's

#### **Progress**

- Background

- Instruction collapsing

- Potential performance improvements

- Limitations of the approach

- Implementation

- Improvements to the approach

- Summary

#### **Implementation**

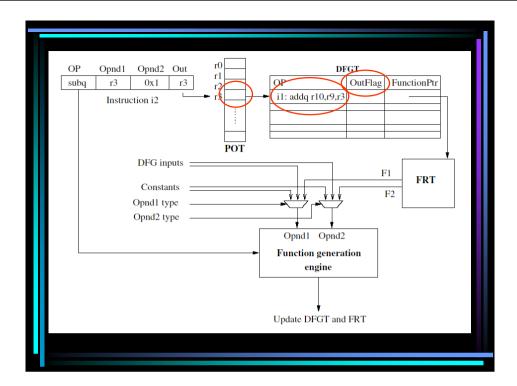

- 4 main components

- DFGT: Data Flow Graph Table

- POT: Producing Output Table

- FGE : Function Generation Engine

- FRT : Function Repository Table

#### **Implementation**

- Output flag set to indicate which instruction is an output of the DFGT

- Use the POT to keep track of data dependencies

- Each entry has an index into the DFGT to the instruction that produces the result for that register

- The combination of the POT and DFGT is similar to that of the ROB, except that it is done offline

- Once an instruction is loaded into the DFGT, compose this operation with the functions producing its source operands, thus creating a more complex function

#### Implementation

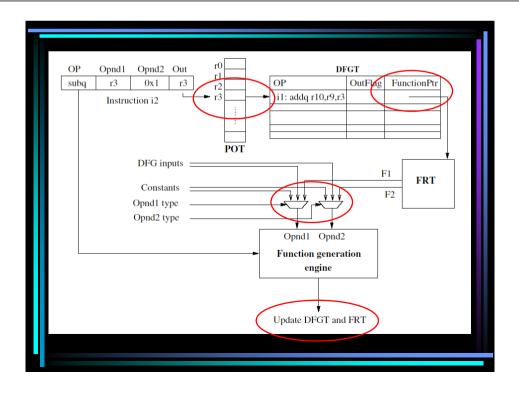

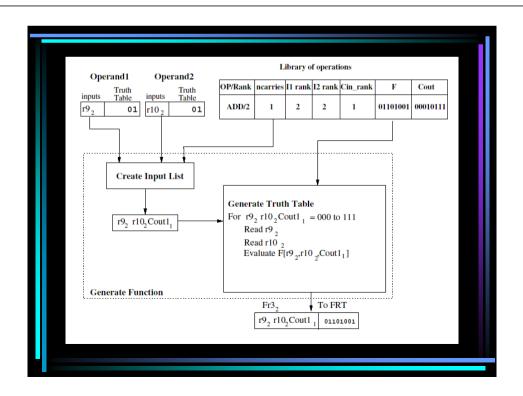

- FGE (Function Generation Engine)

- Three types of inputs

- If the operand is a result of a previous instruction, send the function producing this operand as a truth table

- FRT (Function Repository Table)

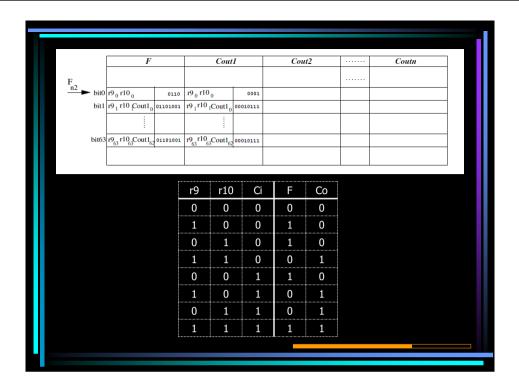

- Stores the result of each function as a 64 bit truth table (6 inputs for each function)

- One truth table for EACH bit of the input word

- Each entry in the DFGT contains an index to the corresponding function results in the FRT

- Also stores the number of inputs of the truth table

#### **Implementation**

- How does the FGE create a new truth table from the previous ones?

- For each combination of the inputs, it looks up the truth table of the operands

- Uses the result to look up the truth table of the operation itself (this is stored in an additional library of operations)

- The library also indicates if additional variables (ie carries) must be introduced

- The final function truth table is stored back into the FRT, and linked through the DFGT again

### Hardware implementation

- From truth table to reconfigurable Function Unit

- Function unit advantages

- Combinational logic only

- Single row

- No complex interconnections

- Disadvantages

- Significant number of inputs → large logic blocks

#### Hardware implementation

- Major issue

- Overhead of dynamically building DFG's and functions on the fly

- Assembling large traces

- Trace → DFG → Function truth table → Macro

- rePLay framework

- Not going into details

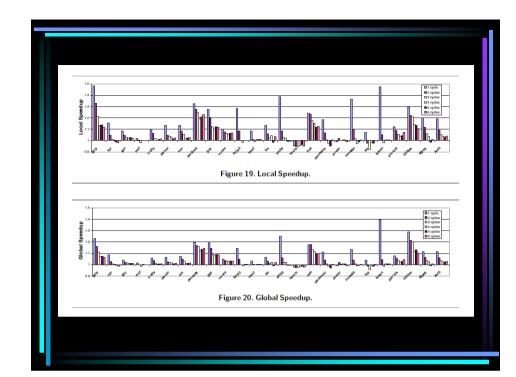

- Speed up of branch resolution

- Effect of Function delay (reconfig and process)

#### **Progress**

- Background

- Instruction collapsing

- Potential performance improvements

- Limitations of the approach

- Implementation

- Improvements to the approach

- Summary

• Increase the number of inputs?

- Increase trace window for frames?

- Alleviate load cuts through address prediction?

- Combine Functions with existing ILP techniques

- Best of both worlds

## Summary

- Exploits circuit level parallelism

Collapse dependent instructions into 2 level combinational circuits

- Works independently of ILP

Targets a different set of instructions