# Learning Outcomes

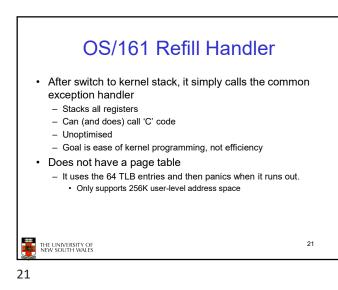

- An understanding of TLB refill:

- in general,

- and as implemented on the R3000

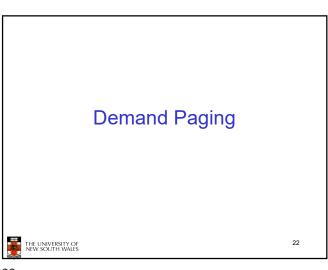

- An understanding of demand-paged virtual memory in depth, including:

2

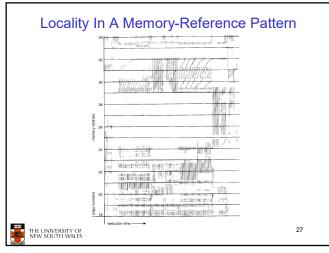

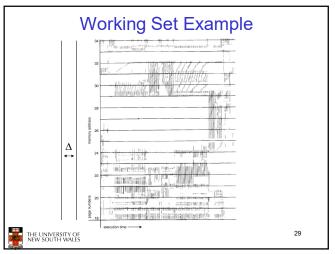

- Locality and working sets

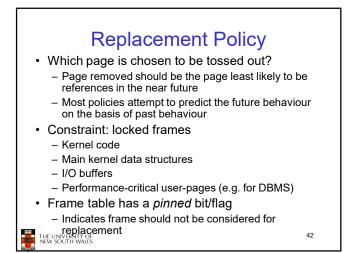

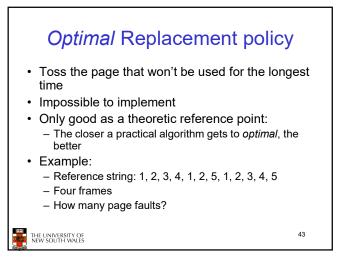

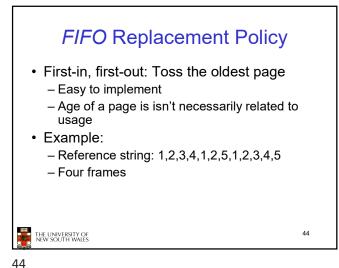

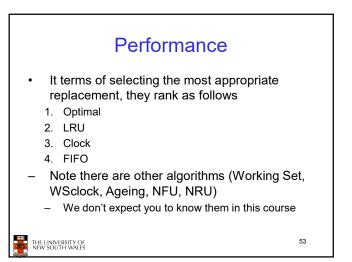

- Page replacement algorithms

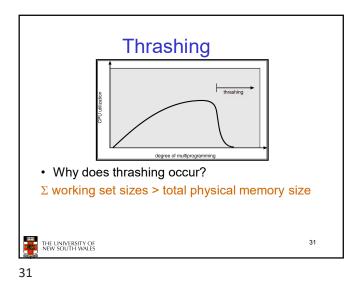

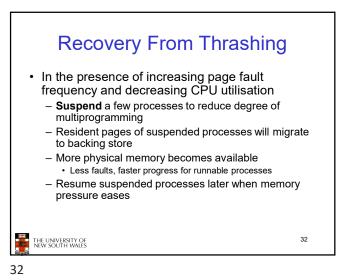

- Thrashing

### THE UNIVERSITY OF NEW SOUTH WALES

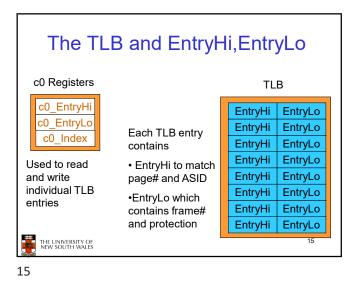

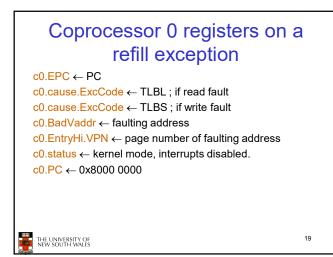

| C                                                                                                                                                    | :0 Re   | gis  | ter                                             | S               |                 |         |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------------------------------------------------|-----------------|-----------------|---------|---------|

| 31                                                                                                                                                   | 12      | 11   |                                                 |                 | 6               | 5       | 0       |

| VPN                                                                                                                                                  |         | ASID |                                                 |                 |                 | 0       |         |

| EntryHi Register (TLB key fields)                                                                                                                    |         | •    |                                                 |                 |                 |         |         |

| 31                                                                                                                                                   | 12      | 11   | 10                                              | 9               | 8               | 7       | 0       |

| PFN                                                                                                                                                  |         | Ν    | D                                               | V               | G               | 0       |         |

| <ul> <li>EntryLo Register (TLB data fields)</li> <li>N = Not cacheab</li> <li>D = Dirty = Write</li> <li>G = Global (ignor<br/>in lookup)</li> </ul> | protect | • 6  | / = val<br>64 TLB<br>Access<br>Coproc<br>– Entr | entri<br>ed via | a soft<br>0 reg | gisters | through |

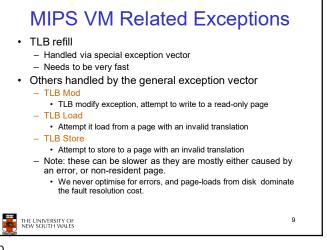

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

THE UNIVERSITY OF NEW SOUTH WALES

THE UNIVERSITY OF NEW SOUTH WALES

| Honeywell/Multics | 1K words (36-bit)              |  |  |

|-------------------|--------------------------------|--|--|

| IBM 370/XA        | 4K bytes                       |  |  |

| DEC VAX           | 512 bytes                      |  |  |

| IBM AS/400        | 512 bytes                      |  |  |

| Intel Pentium     | 4K and 4M bytes                |  |  |

| ARM               | 4K and 64K bytes               |  |  |

| MIPS R4000        | 4k – 16M bytes in powers of 4  |  |  |

| DEC Alpha         | 8K - 4M bytes in powers of 8   |  |  |

| UltraSPARC        | 8K – 4M bytes in powers of 8   |  |  |

| PowerPC           | 4K bytes + "blocks"            |  |  |

| Intel IA-64       | 4K – 256M bytes in powers of 4 |  |  |

## New New

<section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><table-container>

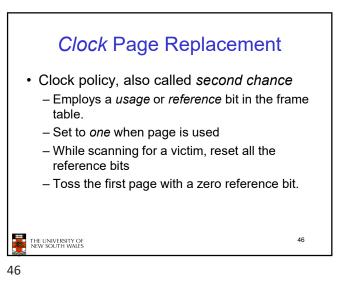

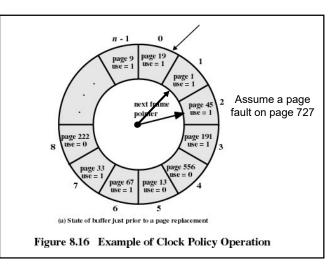

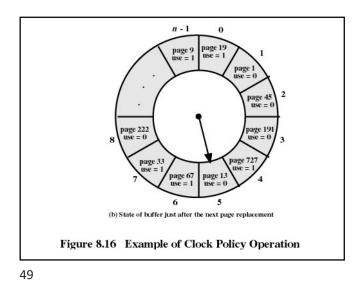

(a) State of buffer fust prior to a page replacement Figure 8.16 Example of Clock Policy Operation

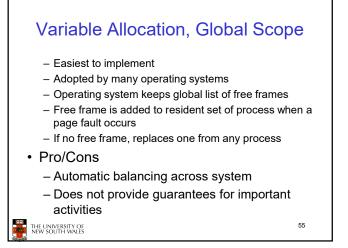

# Variable Allocation, Local Scope

- Allocate number of page frames to a new process based on

- Application type

- Program request

- Other criteria (priority)

- When a page fault occurs, select a page from among the resident set of the process that suffers the page fault

56

• Re-evaluate allocation from time to time!

THE UNIVERSITY OF NEW SOUTH WALES

56