# **Computer System Overview**

**Operating Systems**

2005/S2

What are the objectives of an Operating System?

#### What are the objectives of an Operating System?

- $\rightarrow$  convenience & abstraction

- the OS should facilitate the task of application and system programmer

- hardware details should be hidden, uniform interface for different I/O devices provided

- ➔ efficiency

should take up few resources, make good use of resources, and be fast

#### $\rightarrow$ protection

fairness, security, safety

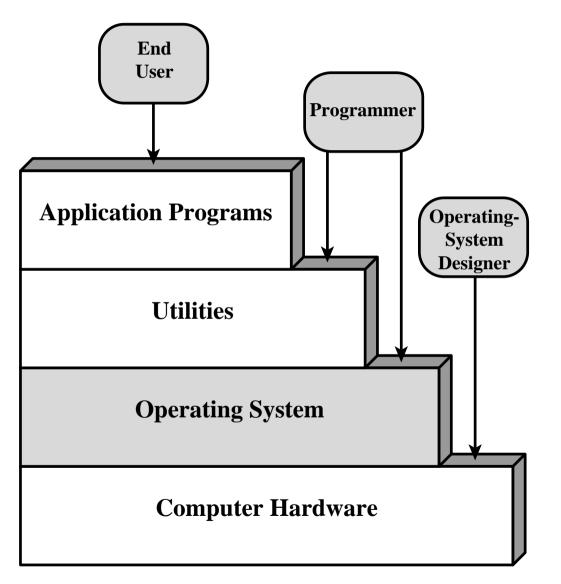

# LAYERS OF A COMPUTER SYSTEM

Simplified view:

➔ Processor

Simplified view:

- → Processor

- → Main Memory

- referred to as real memory or primary memory

- volatile

Simplified view:

- → Processor

- → Main Memory

- referred to as real memory or primary memory

- volatile

- → I/O modules

- secondary memory devices

- communications equipment

- terminals

Simplified view:

- → Processor

- → Main Memory

- referred to as real memory or primary memory

- volatile

- → I/O modules

- secondary memory devices

- communications equipment

- terminals

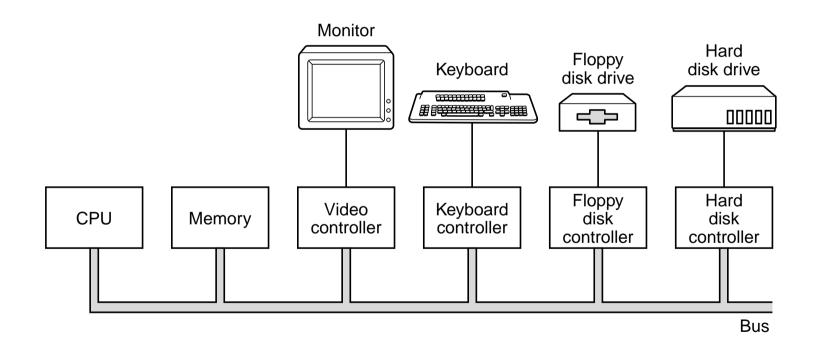

- $\rightarrow$  System bus

- communication among processors, memory, and I/O modules

## **TOP-LEVEL COMPONENTS**

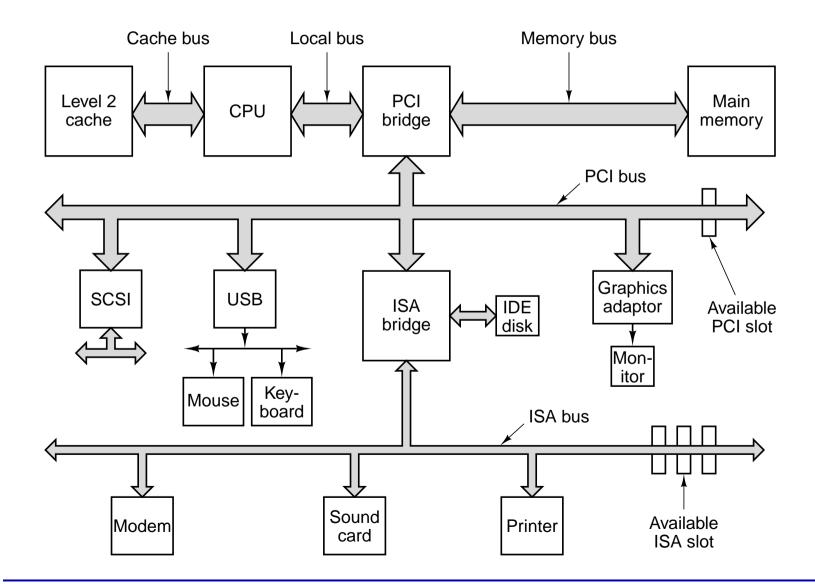

#### **EXAMPLE: LARGE PENTIUM SYSTEM**

EXAMPLE: LARGE PENTIUM SYSTEM

## PROCESSOR

- $\rightarrow$  Fetches intructions from memory, decodes and executes them

- → Set of instructions is processor specific

# PROCESSOR

- $\rightarrow$  Fetches intructions from memory, decodes and executes them

- $\rightarrow$  Set of instructions is processor specific

- $\rightarrow$  Instructions include:

- ★ load value from memory into register

- ★ combine operands from registers or memory

- ★ branch

## PROCESSOR

- $\rightarrow$  Fetches intructions from memory, decodes and executes them

- → Set of instructions is processor specific

- $\rightarrow$  Instructions include:

- ★ load value from memory into register

- ★ combine operands from registers or memory

- ★ branch

- → All CPU's have registers to store

- $\star$  key variables and temporary results

- ★ information related to control program execution

## **PROCESSOR REGISTERS**

- → Data and address registers

- Hold operands of most native machine instructions

- Enable programmer to minimize main-memory references by optimizing register use

- user-visible

## **PROCESSOR REGISTERS**

- → Data and address registers

- Hold operands of most native machine instructions

- Enable programmer to minimize main-memory references by optimizing register use

- user-visible

- → Control and status registers

- Used by processor to control operating of the processor

- Used by operating-system routines to control the execution of programs

- Sometimes not accessible by user (architecture dependent)

# USER-VISIBLE REGISTERS

- → May be referenced by machine language instructions

- Available to all programs application programs and system programs

- $\rightarrow$  Types of registers

- Data

- Address

- Index

- Segment pointer

- Stack pointer

- Many architectures do not distinguish different types

→ Program Counter (PC)

- → Program Counter (PC)

- Contains the address of an instruction to be fetched

- → Program Counter (PC)

- Contains the address of an instruction to be fetched

- $\rightarrow$  Instruction Register (IR)

- → Program Counter (PC)

- Contains the address of an instruction to be fetched

- $\rightarrow$  Instruction Register (IR)

- Contains the instruction most recently fetched

- → Program Counter (PC)

- Contains the address of an instruction to be fetched

- $\rightarrow$  Instruction Register (IR)

- Contains the instruction most recently fetched

- → Processor Status Word (PSW)

- → Program Counter (PC)

- Contains the address of an instruction to be fetched

- $\rightarrow$  Instruction Register (IR)

- Contains the instruction most recently fetched

- → Processor Status Word (PSW)

- condition codes

- interrupt enable/disable

- supervisor/user mode

- $\rightarrow$  Condition Codes or Flags

- Bits set by the processor hardware as a result of operations

- Can be accessed by a program but not altered

- Examples

- positive/negative result

- zero

- overflow

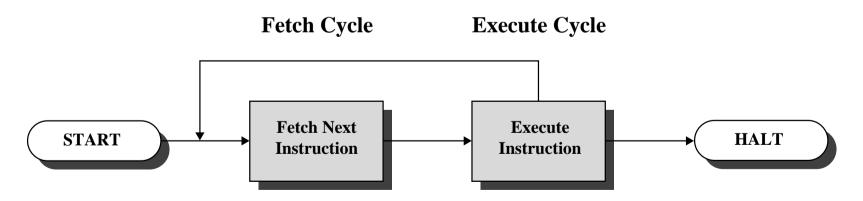

# **INSTRUCTION FETCH AND EXECUTE**

- Program counter (PC) holds address of the instruction to be fetched next

- → The processor fetches the instruction from memory

- → Program counter is incremented after each fetch

- → Overlapped on modern architectures (pipelining)

#### **INSTRUCTION REGISTER**

- $\rightarrow$  Fetched instruction is placed in the instruction register

- $\rightarrow$  Types of instructions

- Processor-memory

- transfer data between processor and memory

- Processor-I/O

- data transferred to or from a peripheral device

- Data processing

- arithmetic or logic operation on data

- Control

- alter sequence of execution

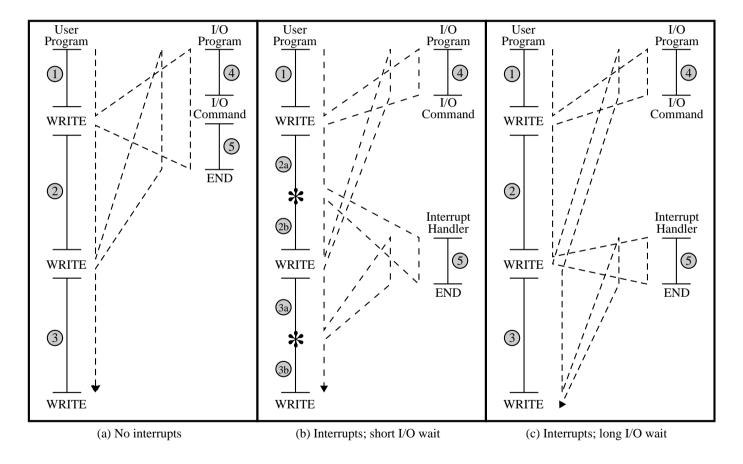

# INTERACTION BETWEEN PROCESSOR AND I/O DEVICES

#### $\rightarrow$ CPU much faster than I/O devices

## INTERACTION BETWEEN PROCESSOR AND I/O DEVICES

- $\rightarrow$  CPU much faster than I/O devices

- waiting for I/O operation to finish is inefficient

- not feasible for mouse, keyboard

#### INTERACTION BETWEEN PROCESSOR AND I/O DEVICES

- $\rightarrow$  CPU much faster than I/O devices

- waiting for I/O operation to finish is inefficient

- not feasible for mouse, keyboard

- $\rightarrow$  I/O module sends an interrupt to CPU to signal completion

- → Interrupts normal sequence of execution

- → Interrupts are also used to signal other events

## **CLASSES OF INTERRUPTS**

- → Asynchronous (external) events

- I/O

- Timer

- Hardware failure

- → Synchronous interrupts or program exceptions

## **CLASSES OF INTERRUPTS**

- → Asynchronous (external) events

- I/O

- Timer

- Hardware failure

- Synchronous interrupts or program exceptions caused by program execution:

- arithmetic overflow

- division by zero

- execute illegal instruction

- reference outside user's memory space

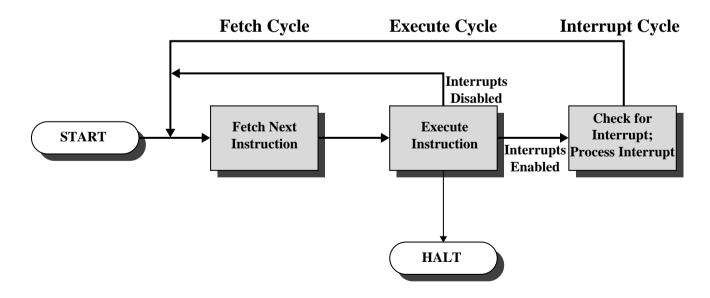

#### INTERRUPT CYCLE

- ① Fetch next instruction

- ② Execute instruction

- 3 Check for interrupt

- ④ If no interrupts, fetch the next instruction

- 5 If an interrupt is pending, divert to the interrupt handler

# **INTERRUPT HANDLER**

- → A program that determines nature of the interrupt and performs whatever actions are needed

- → Control is transferred to this program by the hardware

- → Generally part of the operating system

#### **CONTROL FLOW WITH AND WITHOUT INTERRUPTS**

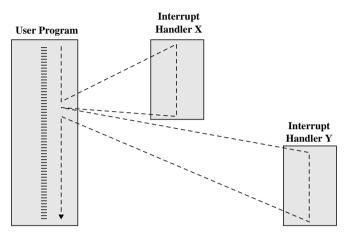

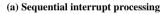

#### **MULTIPLE INTERRUPTS**

- → Interrupt X occurs

- → CPU disables all interrupts (only those with lower priority)

- → Interrupt handler may enable interrupts

- → Interrupt Y occurs

- → Sequential or nested interrupt handling

#### **MULTIPLE INTERRUPTS**

- → Interrupt X occurs

- → CPU disables all interrupts (only those with lower priority)

- → Interrupt handler may enable interrupts

- → Interrupt Y occurs

- → Sequential or nested interrupt handling

(b) Nested interrupt processing

## **MULTIPLE INTERRUPTS**

Sequential Order:

- → Disable interrupts so processor can complete task

- → Interrupts remain pending until the processor enables interrupts

- → After interrupt handler routine completes, the processor checks for additional interrupts

### **MULTIPLE INTERRUPTS**

Priorities:

- → Higher priority interrupts cause lower-priority interrupts to wait

- → Causes a lower-priority interrupt handler to be interrupted

- → Example: when input arrives from communication line, it needs to be absorbed quickly to make room for more input

## MEMORY

#### Sould be

- → fast

- → abundant

- → cheap

# MEMORY

Sould be

- → fast

- → abundant

- → cheap

Unfortunately, that's not the reality...

# MEMORY

Sould be

- → fast

- → abundant

- → cheap

Unfortunately, that's not the reality...

#### Solution:

combination of fast & expensive and slow & cheap memory

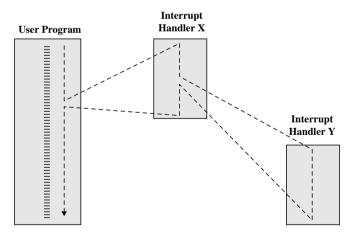

#### MEMORY HIERARCHY

#### **GOING DOWN THE HIERARCHY**

- → Decreasing cost per bit

- $\rightarrow$  Increasing capacity

- $\rightarrow$  Increasing access time

- Decreasing frequency of access of the memory by the processor

Locality of reference is essential!

### **DISK CACHE**

- → A portion of main memory used as a buffer to temporarily to hold data for the disk

- → Disk writes are clustered

- → Some data written out may be referenced again. The data are retrieved rapidly from the software cache instead of slowly from disk

- → Mostly transparent to operating system

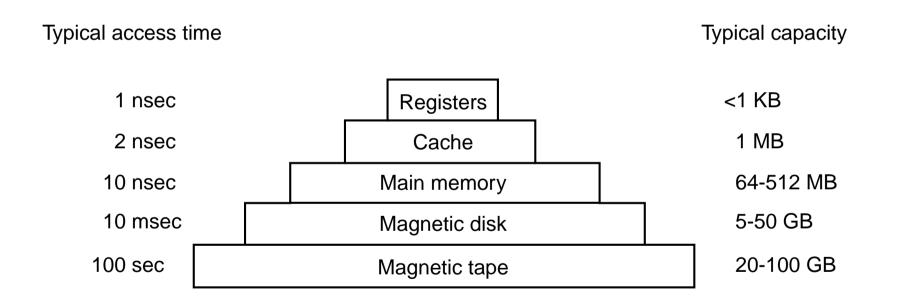

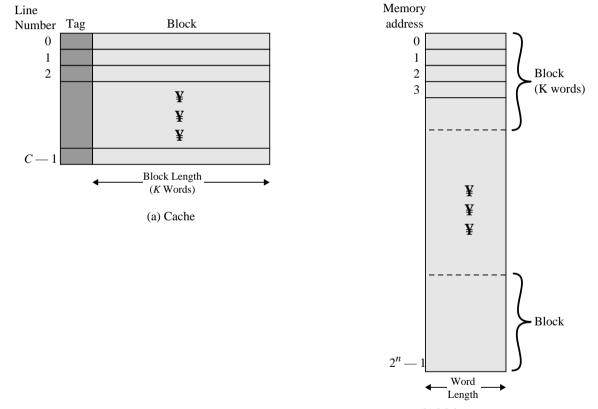

#### CACHE MEMORY

- → Contains a portion of main memory

- → Processor first checks cache

- → If not found in cache, the block of memory containing the needed information is moved to the cache replacing some other data

#### CACHE/MAIN MEMORY SYSTEM

(b) Main memory

## CACHE DESIGN

→ Cache size

- small caches have a significant impact on performance

- → Line size (block size)

- the unit of data exchanged between cache and main memory

- hit means the information was found in the cache

- larger line size ⇒ higher hit rate until probability of using newly fetched data becomes less than the probability of reusing data that has been moved out of cache

### **CACHE DESIGN**

- → Mapping function

- determines which cache location the data will occupy

- → Replacement algorithm

- determines which line to replace

- Least-Recently-Used (LRU) algorithm

- → Write policy

- When the memory write operation takes place

- Can occur every time line is updated (write-through policy)

- Can occur only when line is replaced (write-back policy)

- Minimizes memory operations

- Leaves memory in an obsolete state

#### INTERACTION BETWEEN I/O DEVICES AND PROCESSOR

- → Controller (chip or set of chips) provides a simple interface to OS

- often, embedded OS running on the controller

- $\rightarrow$  Software that communicates with controller is called

INTERACTION BETWEEN I/O DEVICES AND PROCESSOR

- → Controller (chip or set of chips) provides a simple interface to OS

- often, embedded OS running on the controller

- Software that communicates with controller is called device driver

- → Most drivers run in kernel mode

- → To put new driver into kernel, system may have to

- be relinked

- be rebooted

- dynamically load new driver

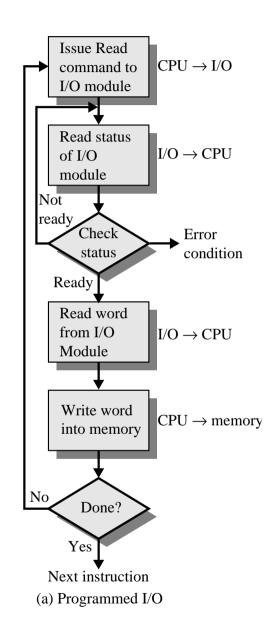

# PROGRAMMED I/O (POLLING)

- → I/O module performs the action, not the processor

- → Sets appropriate bits in the I/O status register

- → No interrupts occur

- → Processor checks status until operation is complete

- Wastes CPU cycles

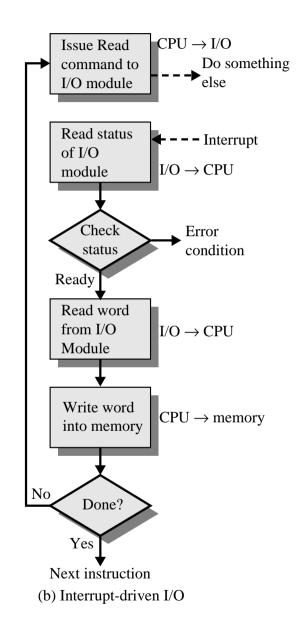

### INTERRUPT-DRIVEN I/O

- → Processor is interrupted when I/O module ready to exchange data

- → Processor is free to do other work

- → No needless waiting

- Consumes a lot of processor time because every word read or written passes through the processor

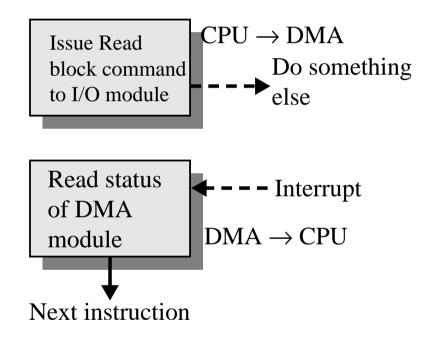

### **DIRECT MEMORY ACCESS**

- → Transfers a block of data directly to or from memory

- → An interrupt is sent when the task is complete

- → The processor is only involved at the beginning and end of the transfer