# **Learning Outcomes**

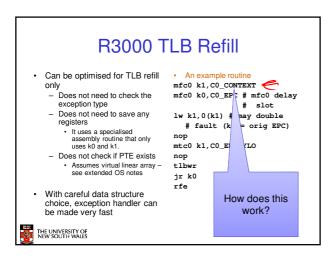

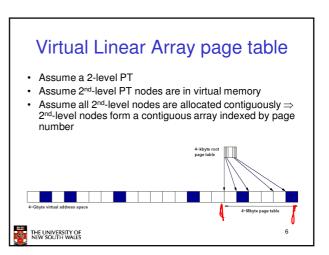

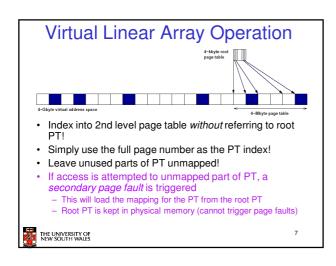

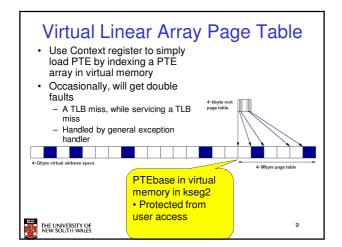

- An understanding of virtual linear array page tables, and their use on the MIPS R3000.

- Exposure to alternative page table structures beyond two-level and inverted page tables.

2

# Design Tradeoffs for Software-Managed TLBs David Nagle, Richard Uhlig, Tim Stanley, Stuart Sechrest Trevor Mudge & Richard Brown

ISCA '93 Proceedings of the 20th annual international symposium on computer architecture

10

# Trends at the time

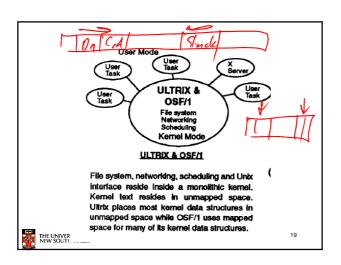

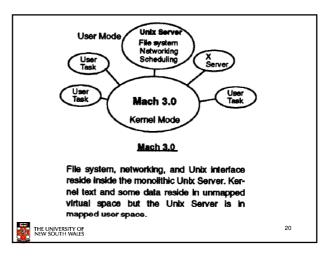

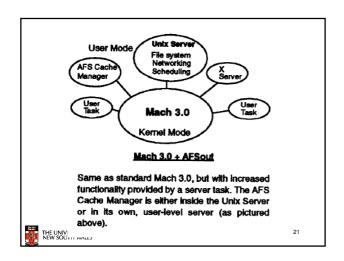

- · Operating systems

- moving functionality into user processes

- making greater use of virtual memory for mapping data structures held within the kernel.

- · RAM is increasing

- TLB capacity is relatively static

- · Statement:

- Trends place greater stress upon the TLB by increasing miss rates and hence, decreasing overall system performance.

- True/False? How to evaluate?

14

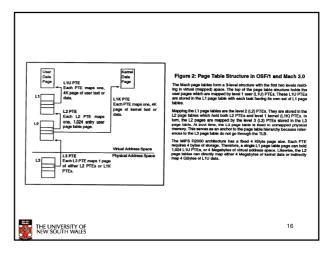

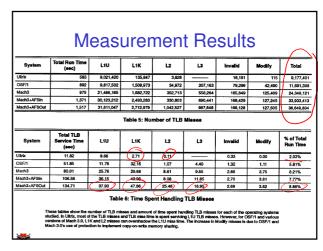

| TLB Miss Type | Ultrix | OSF/1 | Mach 3.0 |

|---------------|--------|-------|----------|

| L1U           | 16     | 20    | 20       |

| L1K           | 333    | 355   | 294      |

| L2            | 494    | 511   | 407      |

| L3            |        | 354   | 286      |

| Modify        | 375    | 436   | 499      |

| Invalid       | 336    | 277   | 267      |

### Table 3: Costs for Different TLB Miss Types

This table shows the number of machine cycles (at 80 ne/cycle) required to service different types of TLB misses. To determine these costs, Monster was used to collect a 128K-entry histogram of timings for each type of miss. We separate TLB miss types into the sk categories described below. Note that Ultrk does not have L3 misses because it implements a 2-level page table.

L1U TLB miss on a level 1 user PTE.

L1K TLB miss on a level 1 kernel PTE.

L2 TLB miss on level 2 PTE. This can only occur after a miss on a level 1 user PTE.

L3 TLB miss on a level 3 PTE. Can occur after either a level 2 miss or a level 1 mismed miss.

THE UNIN Invalid

Modify

A page protection violation.

Invalid

An access to an page marked as invalid (page fault)

# Note the TLB miss costs

• What is expected to be the common case?

18

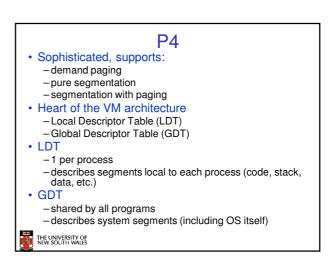

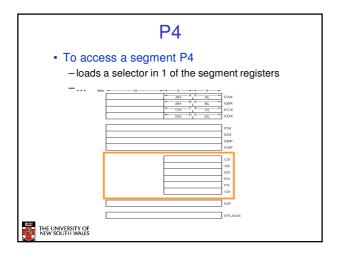

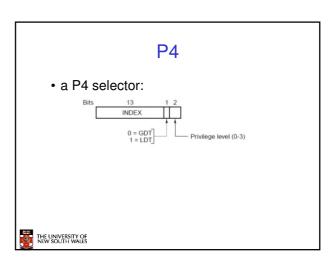

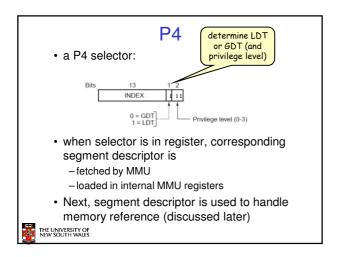

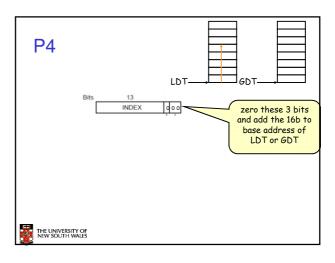

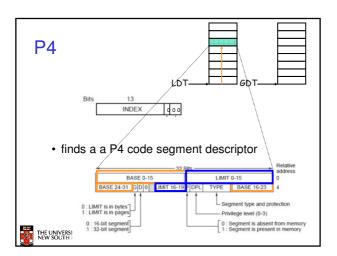

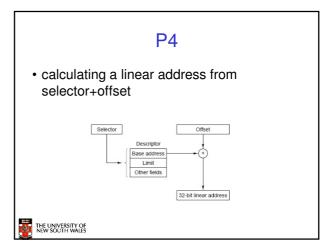

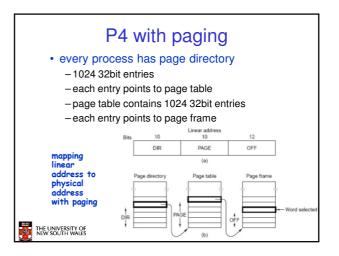

P4

IF no paging used: we are done

→ this is the physical address

ELSE

→ linear address interpreted as virtual address

→ paging again!

# P4 • Many OSs: -BASE=0 -LIMIT=MAX • → no segmentation at all That is it! The UNIVERSITY OF THE